Tool/software:

Hello team,

I have designed output voltage for 5V with feedback resistor and output current is 150mA to 400mA.

I have kept the EN pin floating to turn on the device even with lower voltage.

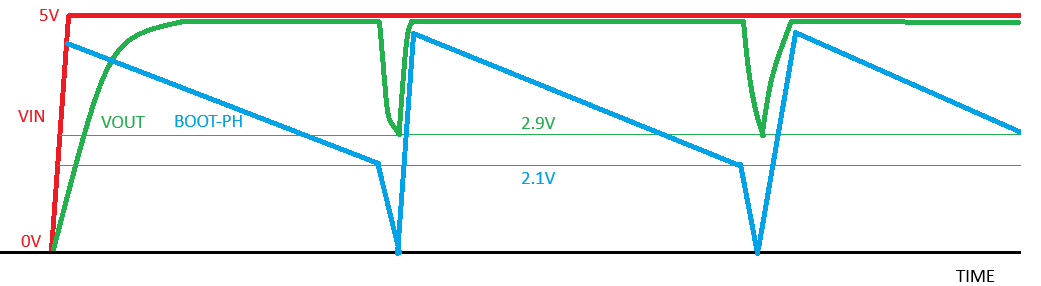

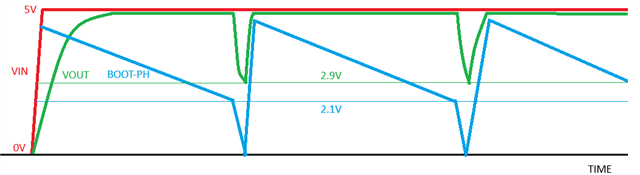

Let's say I apply 5V input for long period, the output voltage will also be nearly 5V as the device operate in 100% duty until BOOT - PH drops below 2.1 V.

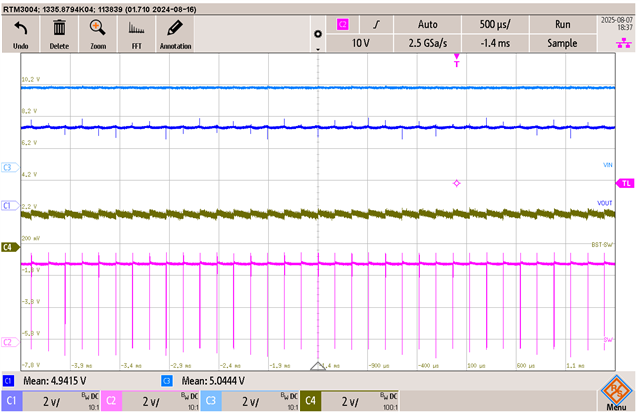

1. Can we determine the rate of discharge of the BOOT capacitor to determine how long the 5V remains constant until the BOOT - PH drops below 2.1 V?

2. When BOOT - PH falls to 2.1V, the MOSFET will turn off and output capacitor starts discharging and when it is 5V-2.1V=2.9V the BOOT -PH rises and output rises 5V so BOOT - PH also rises nearly to 5V. This keeps repeating right if input voltage is constant at 5V. Is my understanding correct? (see graph below and correct if I am wrong)

Thank you,