Other Parts Discussed in Thread: TPS65994BF

Tool/software:

Hi, Sir,

Regarding EC control of the TPS65994BF, we have two questions:

1.Due to power-saving options, sometimes users need to cut off VBUS during sleep mode/hibernate mode/shutdown mode.

On our board, we cut the 5V power at the PP5V pin. However, when PP5V is turned off, the PD sends a reset signal to the retimer,

and the retimer reset causes the CPU to think that a device has been hot-plugged, leading to an unintended wake-up.

(we confirmed that if the reset from the PD to the retimer is disconnected, the system does not wake up automatically).

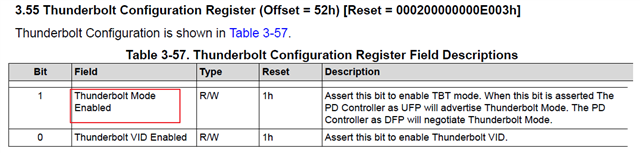

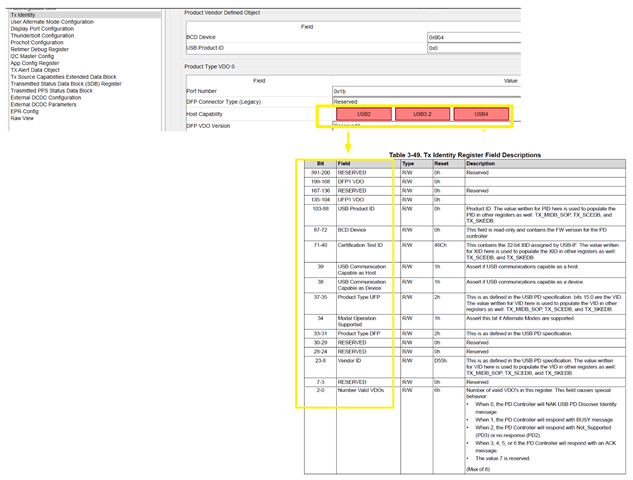

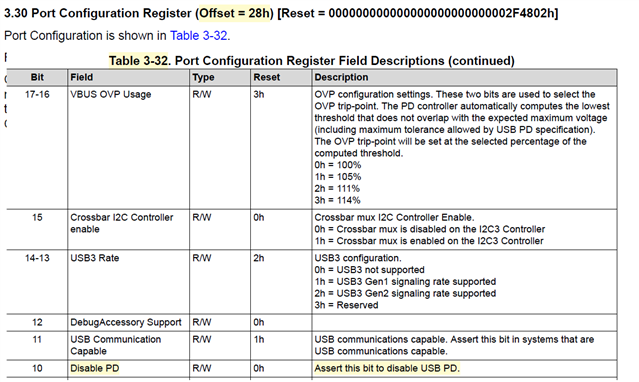

If the EC disables the PD (register is as below) via I2C before entering sleep/hibernate/shutdown mode,

will we avoid TPS65994BF sending the reset signal to the retimer after we cut off PP5V?

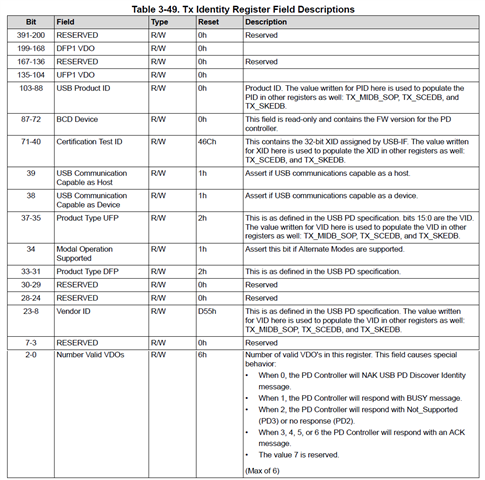

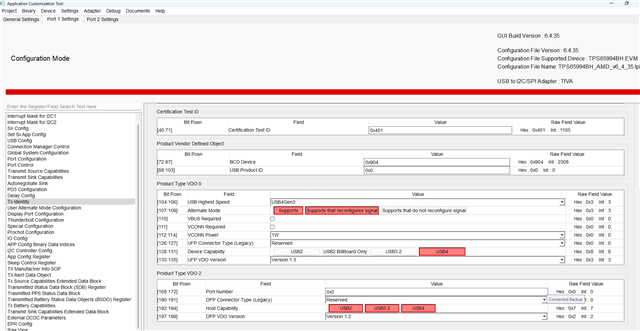

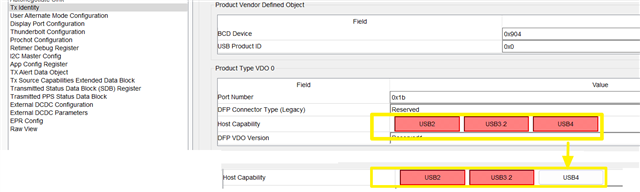

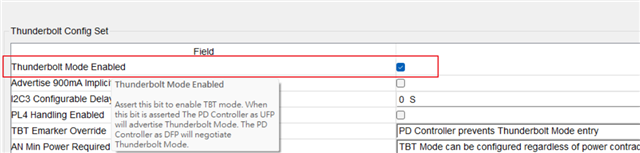

2.The customer is currently planning to implement USB3 Type-C only, but may support USB4 in the future. The BIOS has already disabled Thunderbolt functionality.

However, if the firmware is set to support Thunderbolt and a Thunderbolt cable is connected, the storage device will be identified as a PCIe device and cannot be recognized (since BIOS has disabled Thunderbolt support).

Can we set the firmware to support Thunderbolt, and then use the EC to configure TPS65994BF registers to disable Thunderbolt mode? If this is possible, how should we configure it?

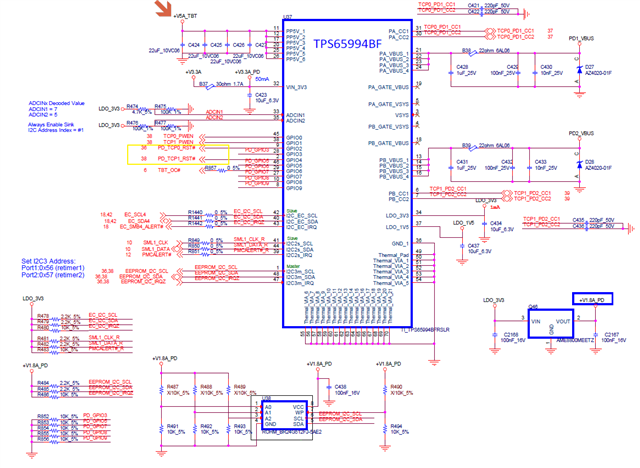

Schematic is as below:

Thanks.