Tool/software:

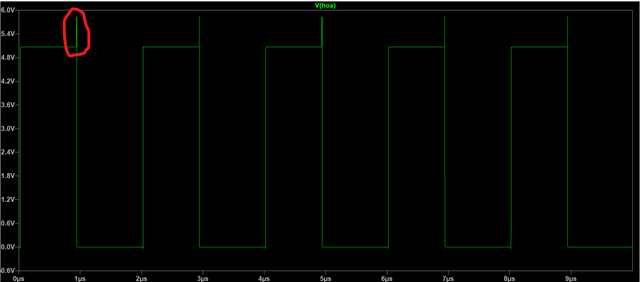

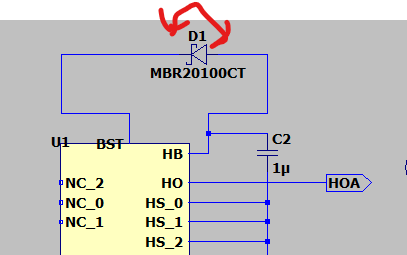

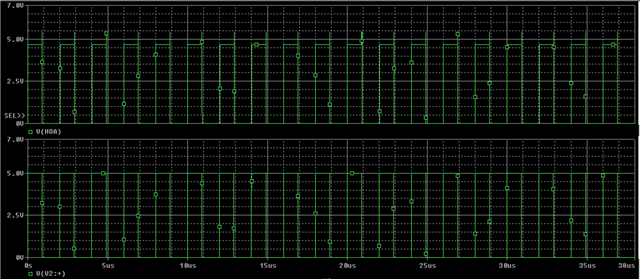

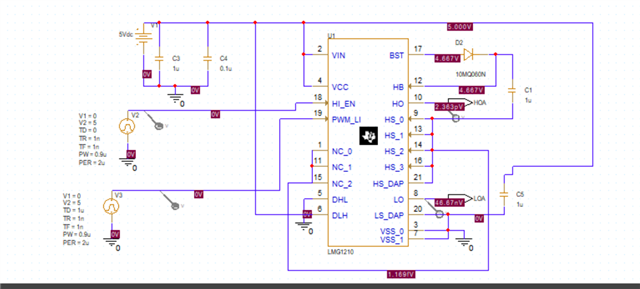

I’m currently simulating the LMG1210 gate driver IC and observing an overshoot at the PWM output during switching. I’ve reviewed the datasheet and application notes but couldn’t pinpoint the root cause.

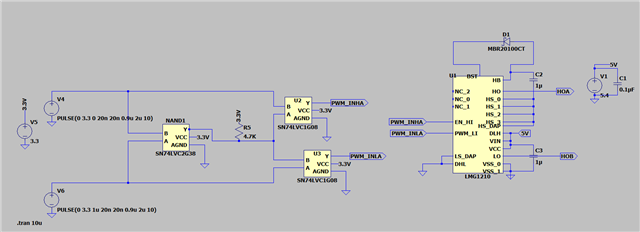

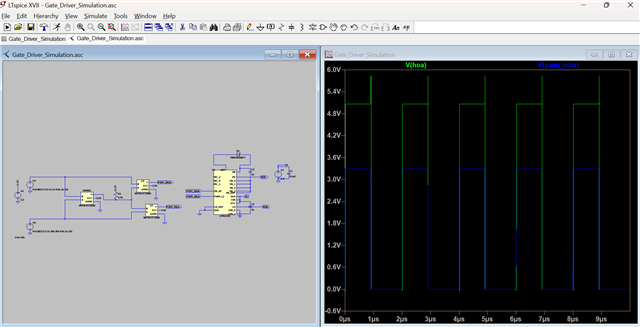

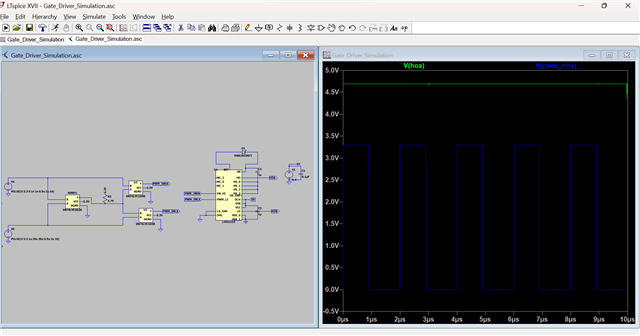

Could you please help me understand why this overshoot is occurring and suggest ways to mitigate it? I’d appreciate any guidance or recommended simulation practices to resolve this issue. I have attached snap of the

LT spice Simulated circuit and Output .