Other Parts Discussed in Thread: BQ41Z90, BQ40Z80, BQSTUDIO

Tool/software:

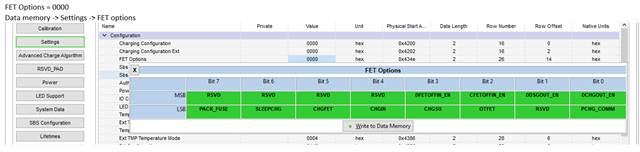

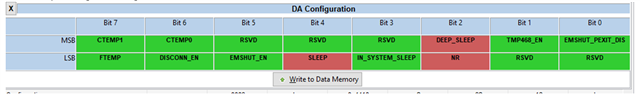

Hi,

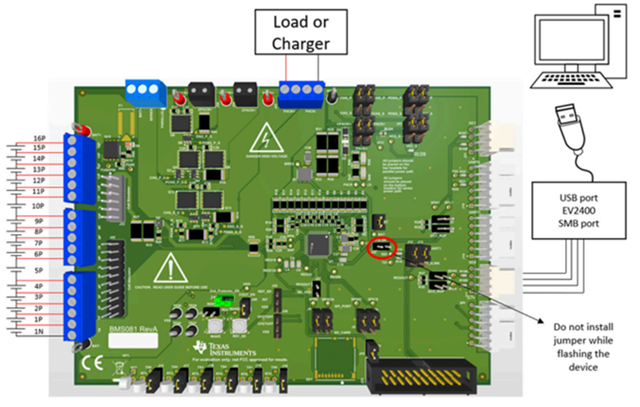

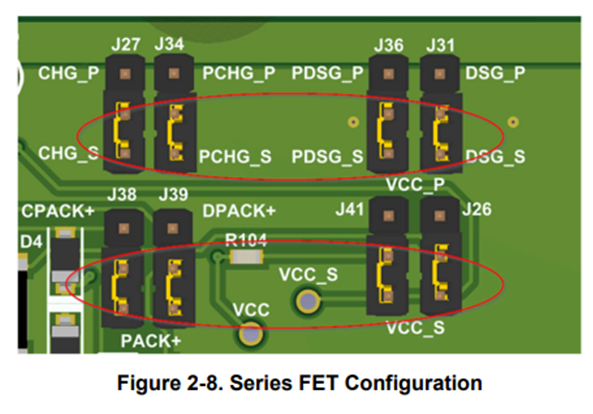

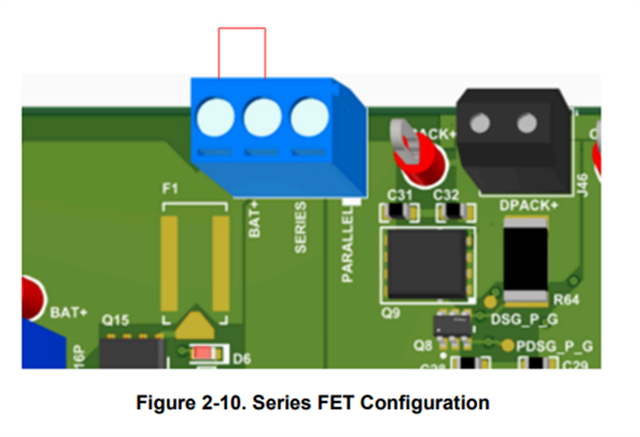

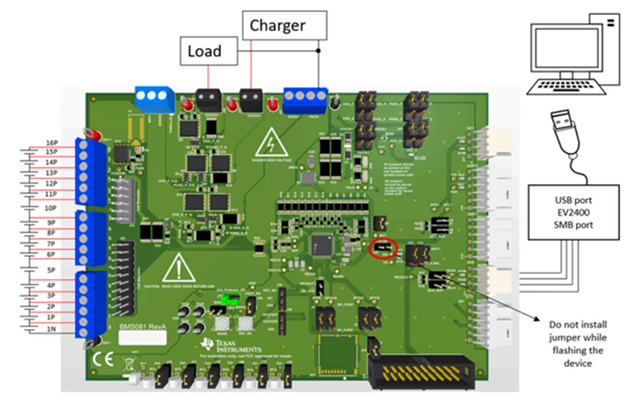

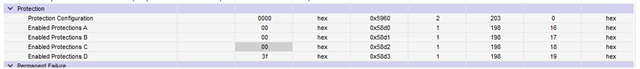

I am busy working with the BQ41Z90 EVM. I am currently struggling to get the charge and the discharge fets to turn on. I have set up the data memory as far as I could but I am unsure if there is something I am missing that keeps the fets from being able to activate.

I have attached the Data Memory files as well as an image of the registers. I would greatly appreciate any assistance in this matter.

Kind Regards

Marco

1212.Registers.gg.csv