Tool/software:

Hello Expert,

Our customer is considering to use TPS1211-Q1.

Then, we'd like to make sure this device's behavior.

In normal operation, they will apply HIGH signal(approx. 3.3V) at EN/UVLO pin from MCU to turn-on FET.

Once TPS1211-Q1 detect fault, MCU detect this fault event and drive EN/UVLO to Low.

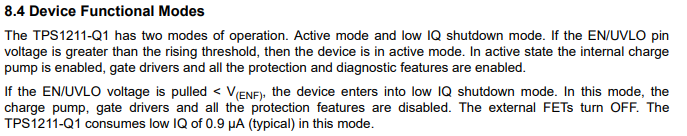

However, their MCU's LOW level approx. 0.4V which is higher than VENF(0.3V) so I'd like to make sure just in case.

In this condition, LOW signal from MCU is still lower than VUVLF(1.1V) so TPS1211-Q1 turn-off FET.

However, Low signal is higher than VENF so we cannot guarantee this device enter low Iq mode.

Is this understanding correct?

Best regards,

Kazuki Kuramochi