Tool/software:

Hi,

My design using the LM27761 is sometimes not working as expected: under certain circumstances it provides an unstable negative output voltage that is way too low.

It is designed to generate -2.7V from a 3.2V source. The load is currently around 280 uA, and needs to be able to go up to around 1 mA.

So far I've tracked it down to the way I power it up:

- If I use the enable button on the lab supply, it starts up as expected.

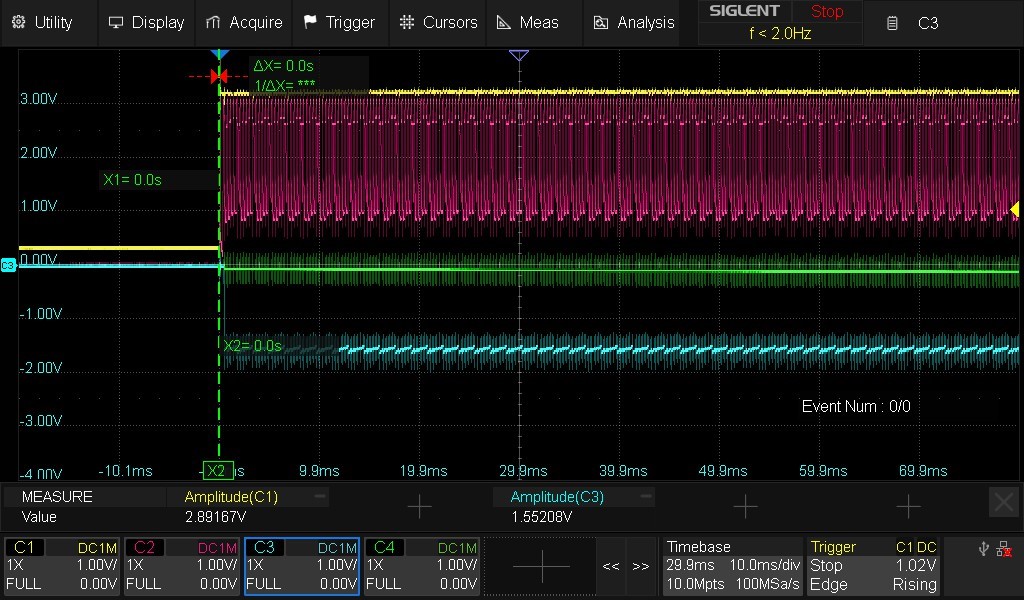

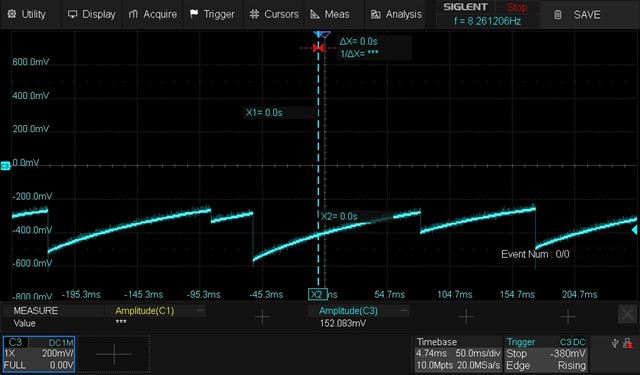

- If I use the jumper connecting VIN (through VDD_NEGRAIL in the schematic), it generates a somewhat wobbly voltage between -200mV and -600mV. It does not recover from this situation unless I cycle the power through the enable button on the lab supply.

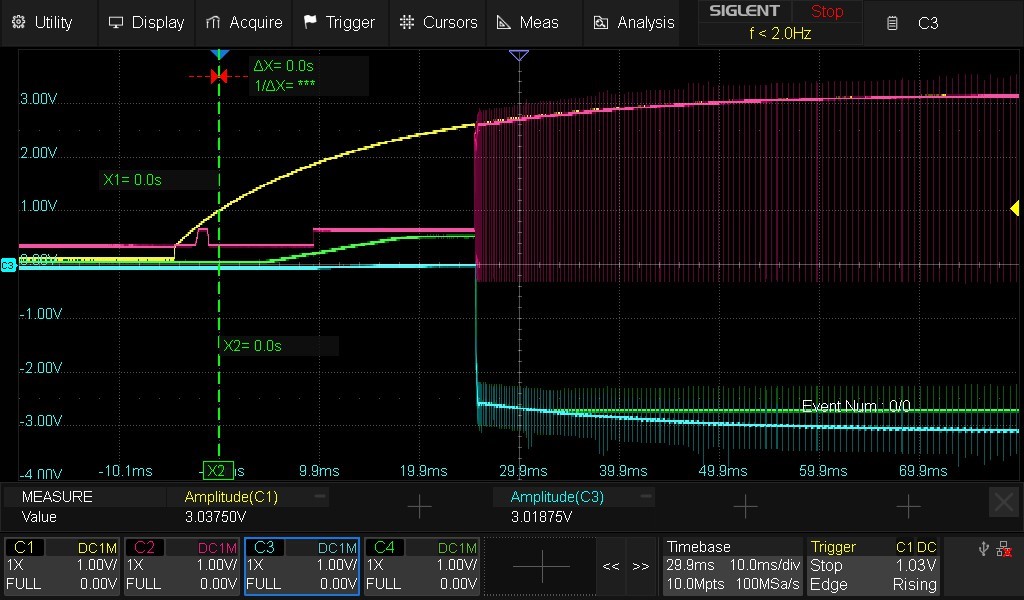

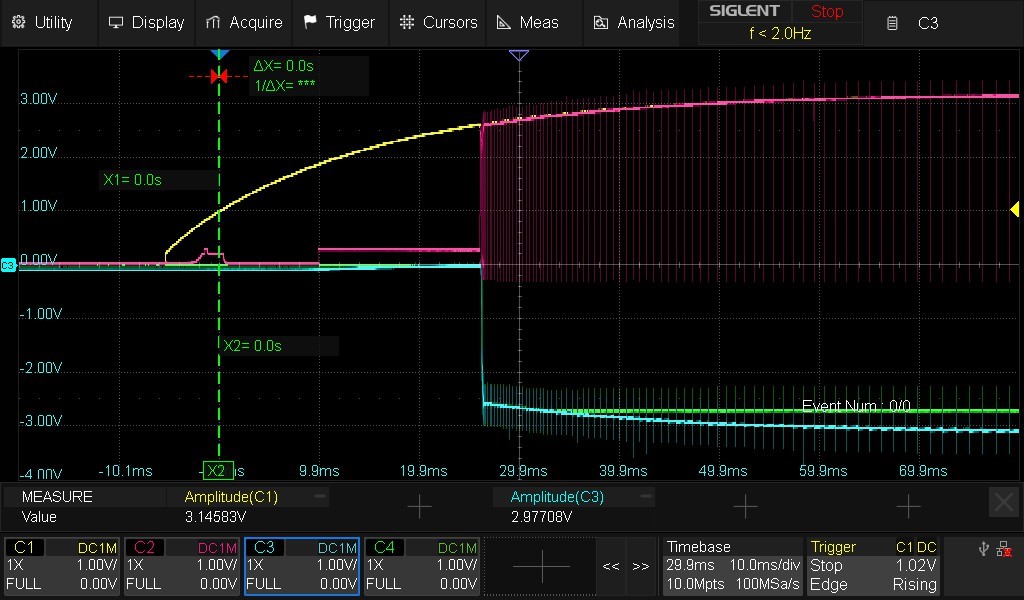

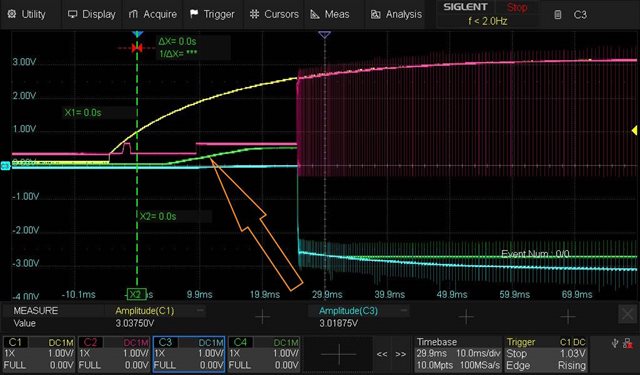

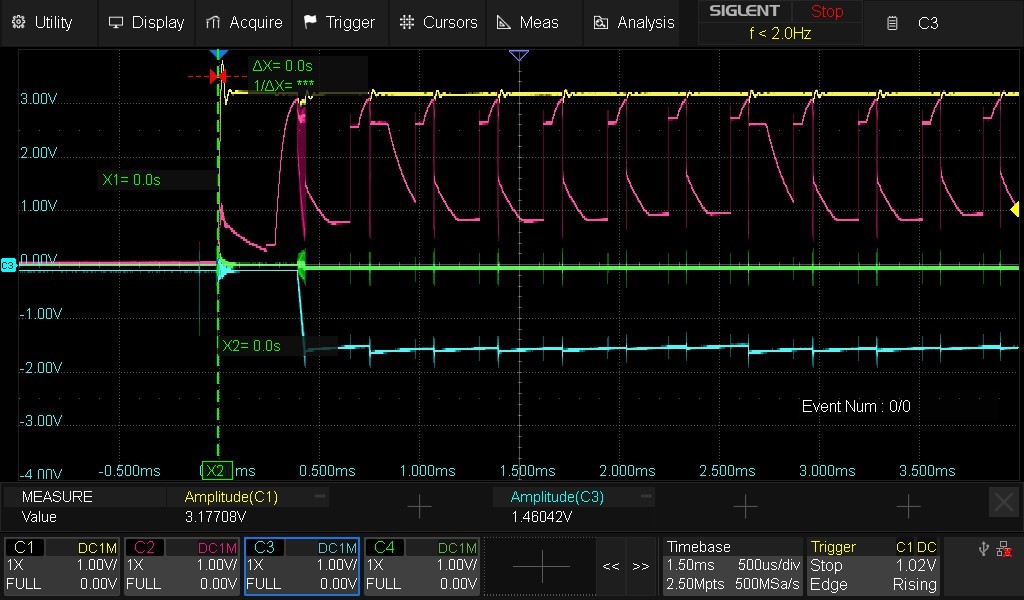

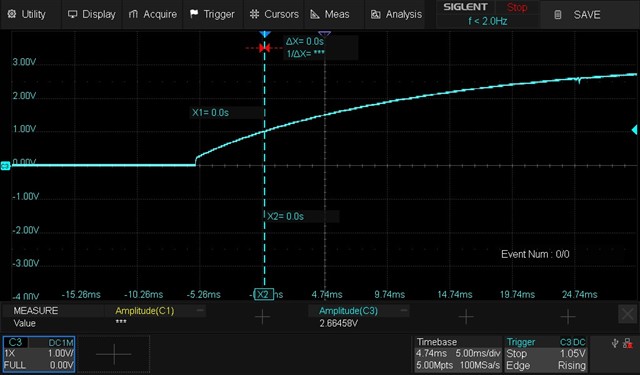

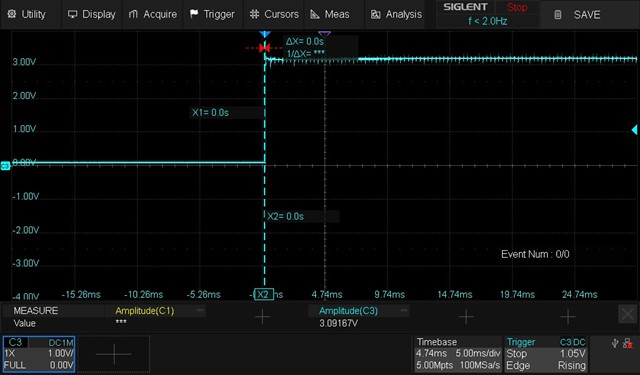

A scope image of the power up event on the VIN pin shows a significant difference on how the voltage rises up on this pin (and I can imagine that this DOES make a difference on the device).

Power up from lab supply

Power up from connecting jumper on VIN

Output when powered up from jumper (power up from lab supply results in normal expected -2.7V output)

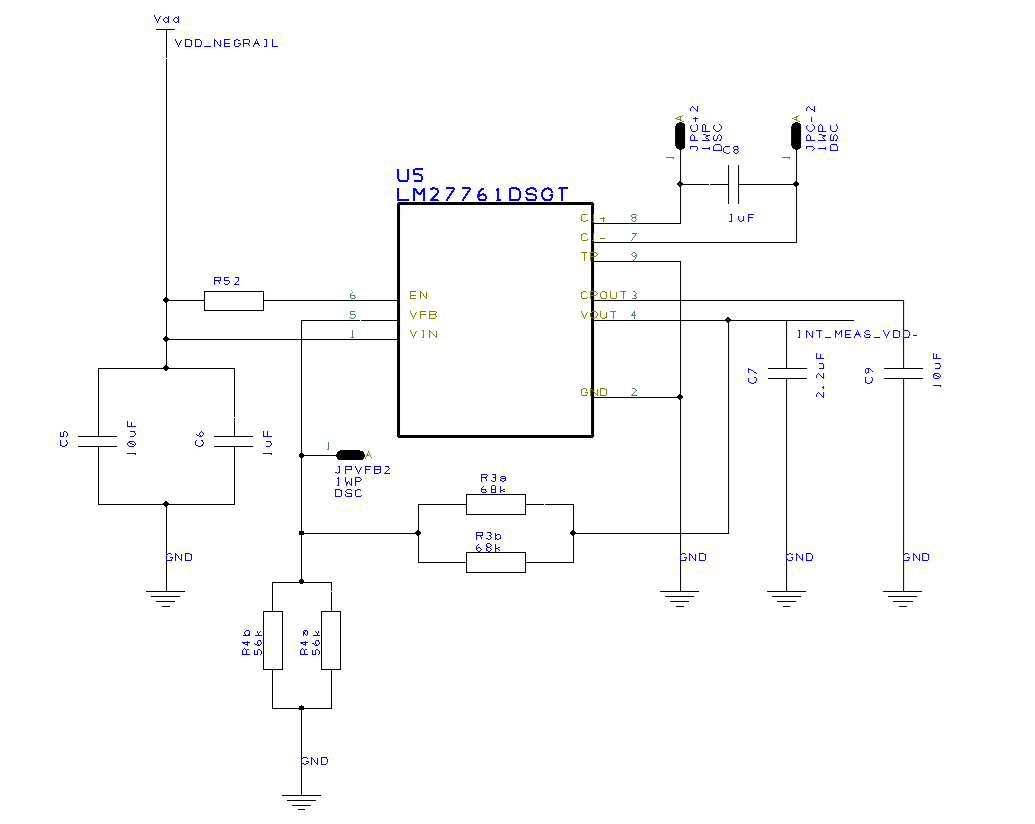

Schematic

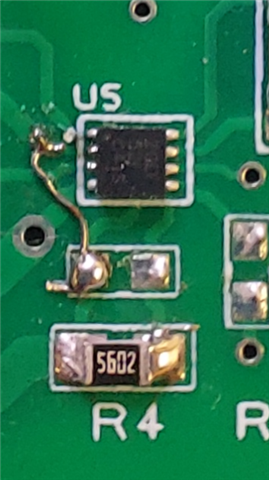

(Please note that R4 and R3 are doubled in the design to accomodate for multiple footprints, only 1 of of each is populated.

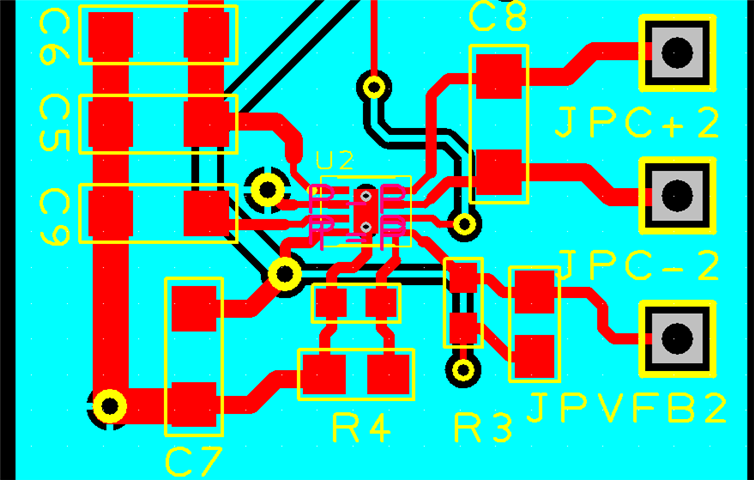

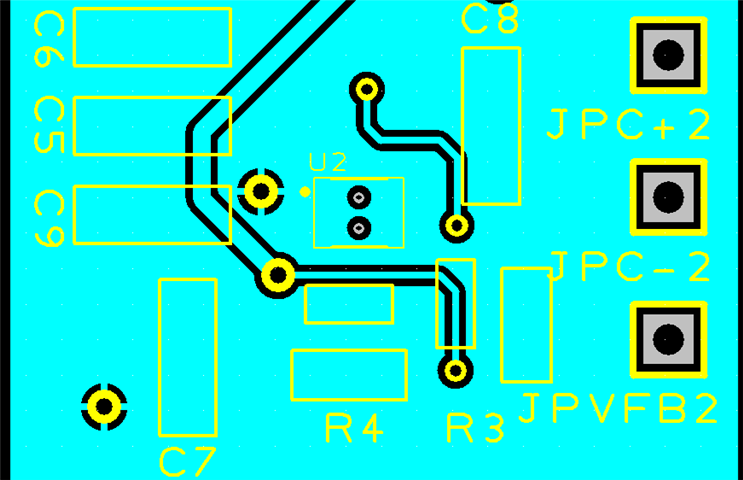

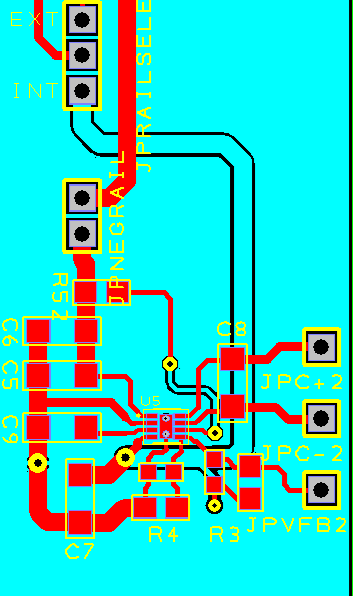

PCB Layout

In my opinion it should work even with the "straight ramp" power up. I have the 27761EVM module that does not have this problem, so it SHOULD be possible to get it correct :-)

The difference between my circuit and that of the EVM is not very big, mainly somewhat different layout directly around the chip and different make of caps and resistors (or so I assume since I don't have P/Ns of what was used on the EVM, but the probability of them being the same is practically zero of course).

Could it be that I need to use slightly different values for my caps or maybe specific parts?

Maybe there are some issues with the layout that could cause this behaviour?

Any help greatly appreciated!

Martin Koster

Sofrides IO