Other Parts Discussed in Thread: TPS7A24

Tool/software:

Hello,

I'm working with TPS76933 LDO. Datasheet shows that there are two variants of this chip available - new and legacy. Table 8-1 shows that new chip has M3 suffix in the name, however in Packing information table there is no any part with M3 in the name. Can somebody confirm that this means that this chip is not in production yet?

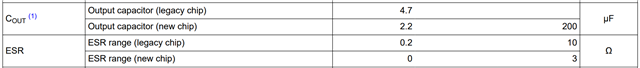

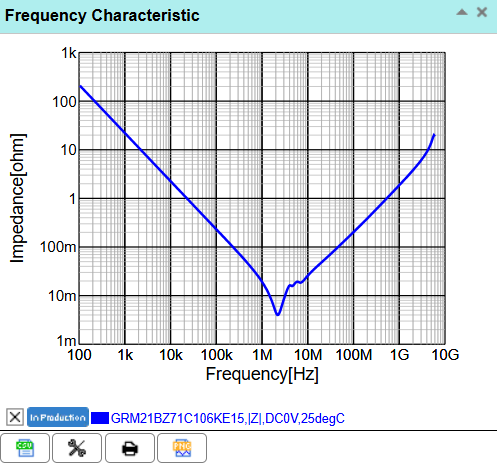

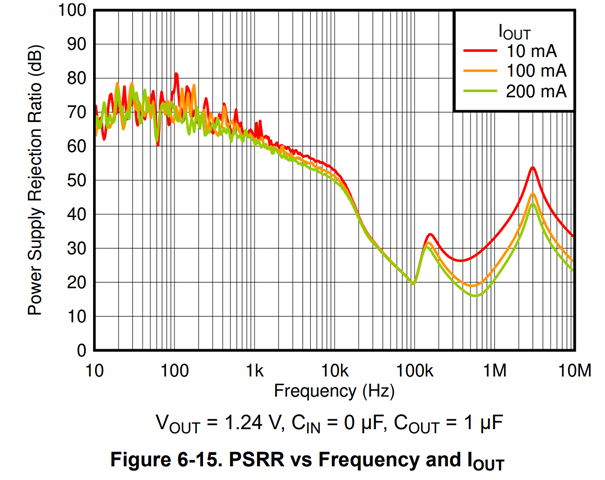

As an output capacitor I'm planing to use 10 uF/16 V capacitor made by Murata, with part number: GRM21BZ71C106KE15L. Should this capacitor work with legacy chip without any additional resistor (like 1 Ohm) added in series?

Thanks!