Other Parts Discussed in Thread: TPS54202

Tool/software:

Hi Team,

<Background>

My customer is checking their field damage issue for SW - GND short (LS FET damage), and they are referring SLUA962 (https://www.ti.com/lit/pdf/slua962) for their issue.

They also have (Vin < Vout) case after power-off period after 1~2sec. For the issue, they have workaround though.

(For TPS54308, VIN = 16.5V, VOUT = 12V, EN = from MCU GPIO)

(For TPS54202 (MCU 5V), VIN = 8.5V, VOUT = 5V, EN = floated)

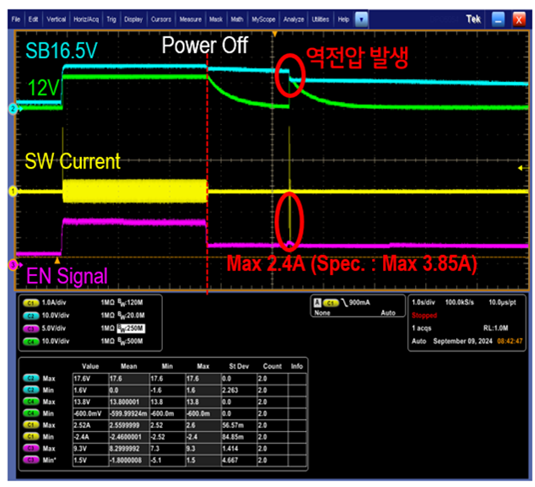

<Figure 1 (Customer waveform 1s/div) : happen Vin < Vout due to abnormal V_EN.>

<Question>

But they want to know more about its root-cause for TPS54308 FCCM mode device.

One question from their side is "Can this FCCM device also be damaged with reverse current?" They think there's LS sink current limit and this is monitored always and turn off the LS FET.

That means both HS and LS are protected by currents monitoring.

Is this thinking correct? If this is correct, then can FCCM or FPWM device be damaged only due to the over voltage spike?

<TPS54308 Current limit>

<Over current protection>

Best Regards,

Ernest Cho