Other Parts Discussed in Thread: PMP22806, , UCC24612

Tool/software:

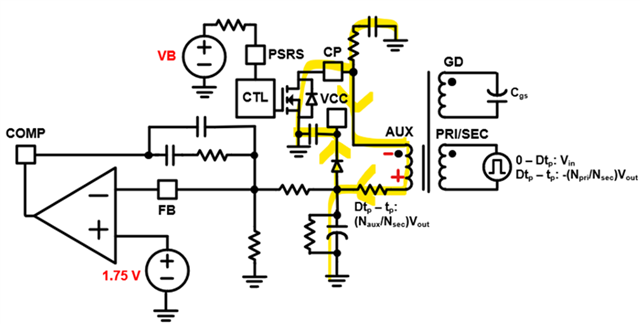

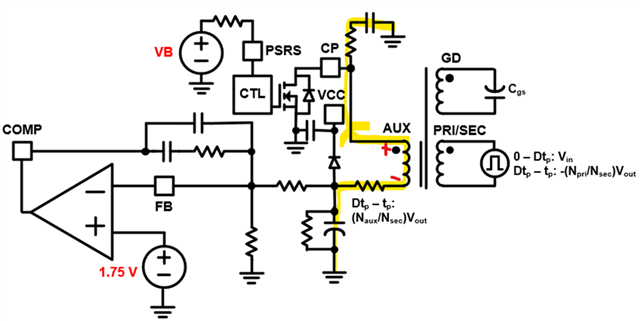

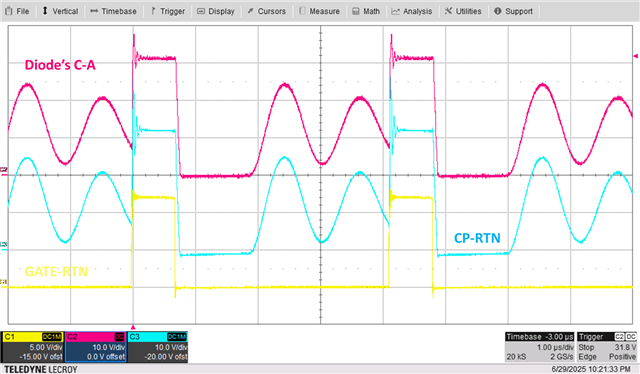

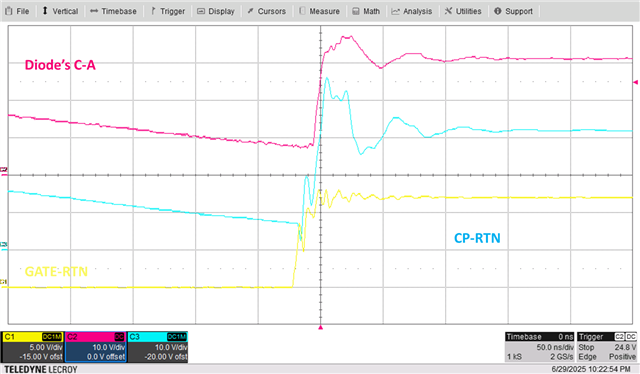

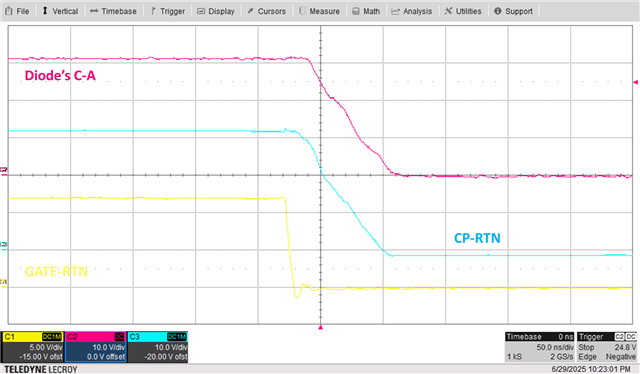

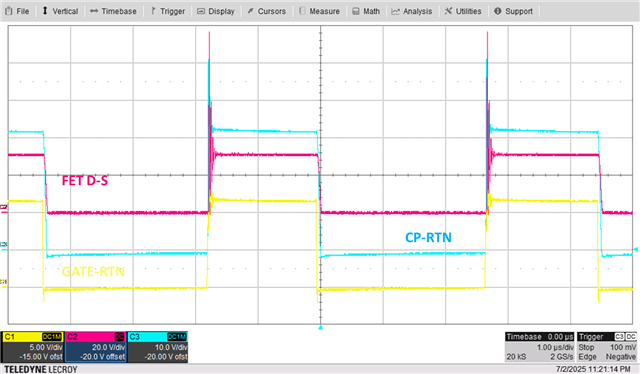

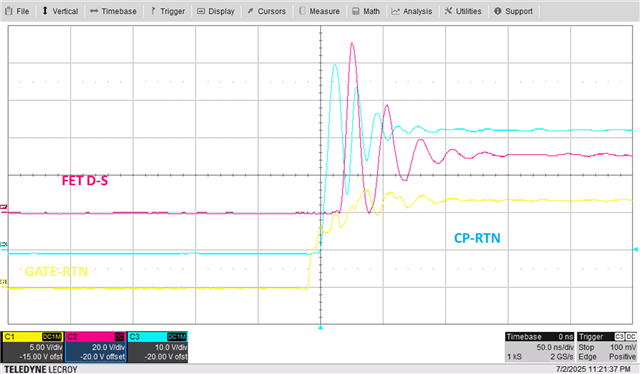

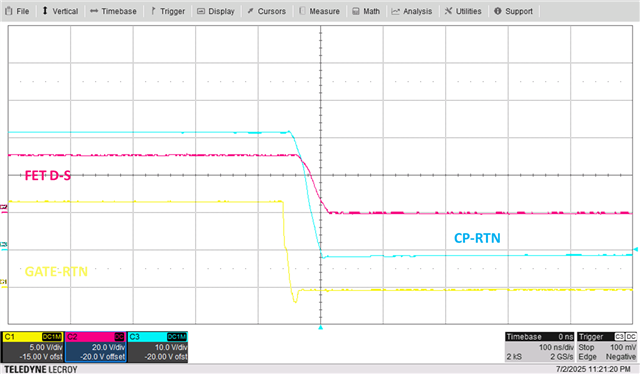

In the related thread (original question), I have questioned whether " actively cancelling (through the use of CP output) the leading-edge voltage overshoot (causing the feedback capacitor to peak-charge)" can be truly postulated. Because the body diode conducts immediately as soon as the primary Mosfet is switched off and the leakage inductance spike is thus exposed to the feedback capacitor. But there is a sort of corollary: only if there would be a small delay of the CP-Mosfet being switched on, until that, the nominal winding voltage does not inject current to the capacitor because in the previous cycle the capacitor is charged with the winding voltage during primary switch off-state minus the minimal voltage drop over the "ideal diode" behind the CP terminal. On the start of the next cycle, only the body diode conducts and because the capacitor has not dropped the voltage more than a few mV, the net voltage "available" to the capacitor is lower: winding voltage minus body diode. So in this minimal time interval, the leakage inductance spike may inject some current (limited by the series resistor), but it has no effect. And hence the capacitor voltage is quite accurately sensing the net winding voltage.

But according to my experiments, it seems that any delay at all is hardly detectable. Perhaps any TI-employee could give a specification of it. Of course, a delay should be longer than the spike width in order to obtain best load regulation.

The explanation above could also help in getting a good load regulation also if an ideal diode circuit on the secondary is used as rectifier. The output voltage is (ideally) based on the regulation of the secondary winding voltage when the Mosfet of the ideal diode circuit conducts. But during an initial delay (of say 40 ns) before the Mosfet is switched off, the secondary winding voltage is then approx. 0.6V higher. This would be reflected in the aux (and the primary) winding. And that would well increase the feedback capacitor voltage (effectively lowering the output voltage). But if the CP-Mosfet would also have a delay of no less than the secondary side delay, this effect would actually be neutralized.

So even more it is interesting to know the CP-Mosfet on-delay.

Next question: could a timed control signal applied to PSRS force an extra CP-Mosfet delay? And even a premature stop of CP Mosfet conducting when the voltage on PSRS is set to low? In short: a signal that follows the CP-voltage, with offset shift towards the positive voltage range and a delay onto the positive slope on PSRS. To say it simple: can PSRS be "modulated" by a digital signal or would a built in flip-flop behind PSRS make a continuous digital control impossible?