Other Parts Discussed in Thread: TPS543B20, TPS543C20

Tool/software:

-

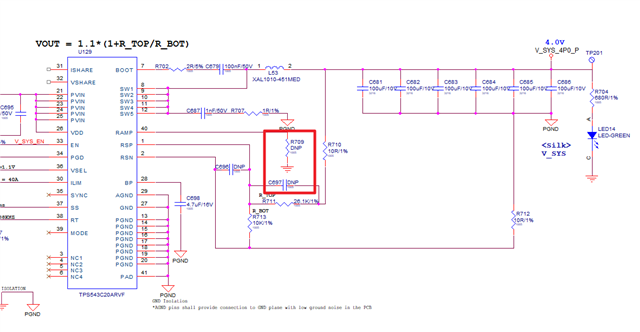

PG Threshold Issue:

-

Product Used: TPS543C20A

-

Set VOUT: 4V (Based on actual schematic, it is 3.971V)

-

Problem Description: When the VOUT drops by approximately 5% to 3.8V due to load fluctuations, the PG (Power Good) signal goes low.

-

Question: What is the reason for the PG activating at -5% instead of the datasheet's specified -10% Undervoltage threshold, and what modifications are needed to adjust it to -12%?

-

-

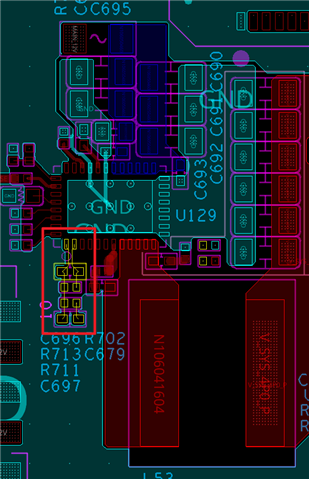

RSP/RSN Wiring Application:

-

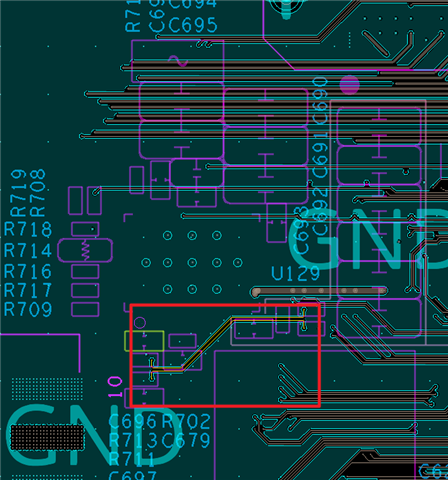

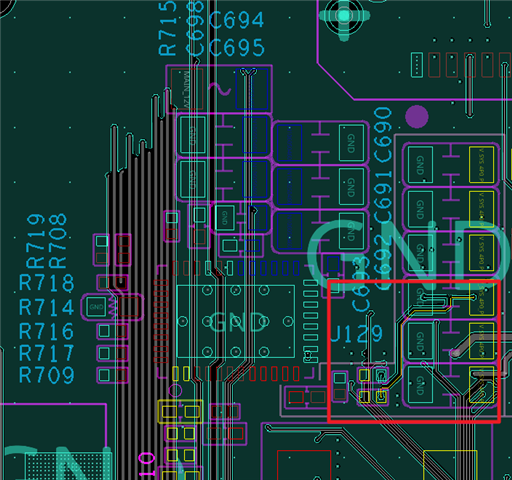

Wiring Application: RSP (Remote Sense Positive) and RSN (Remote Sense Negative) pins were routed with a 100-ohm differential impedance, resulting in thin traces.

-

Question: Can this wiring design cause a misreading of the PG Undervoltage? Please provide guidelines on how to modify the wiring for a more stable design.

-

-

Schematic: Please refer to the attached schematic (

TPS543C20A.pdf). (R_TOP=26.1kΩ, R_BOT=10kΩ) -

File: The

TPS543B20_TPS543C20A_TPS543C20_Calculator-231113.xlsxfile was also referenced. -

VREF: VREF is set to 1.1V.

TOP : RSP, RSN

TOP : RSP, RSN

Regarding R713 and R711 Wiring on Inner Layers

Regarding R713 and R711 Wiring on Inner Layers

Regarding R710, R712, and VOUT Cap Connections

Regarding R710, R712, and VOUT Cap Connections