Other Parts Discussed in Thread: LM25066,

Tool/software:

Hi

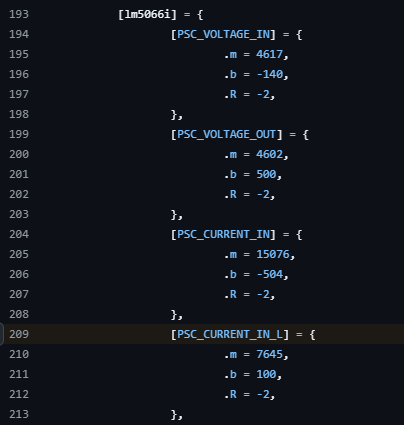

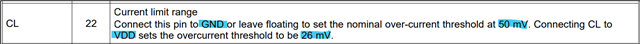

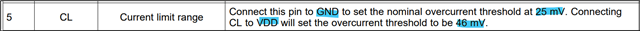

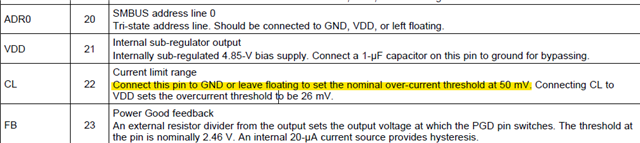

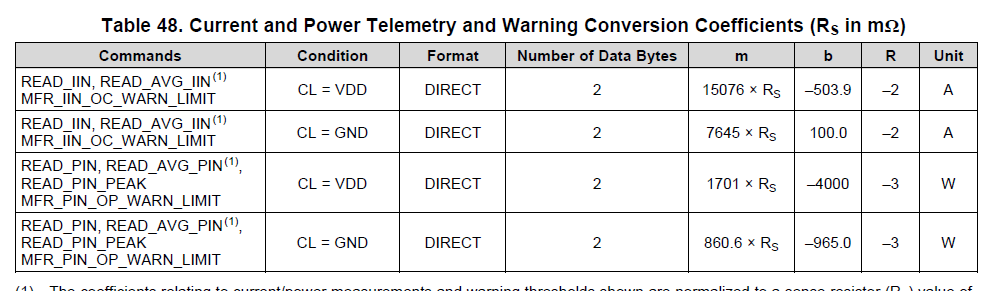

In the hardware circuit, the CL pin is floating, so according to the datasheet, CL = 50 mV. When CL=GND, READ_IIN => m=7645 * Rs; b=100.0; R=-2.

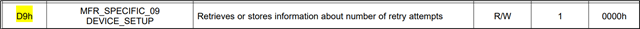

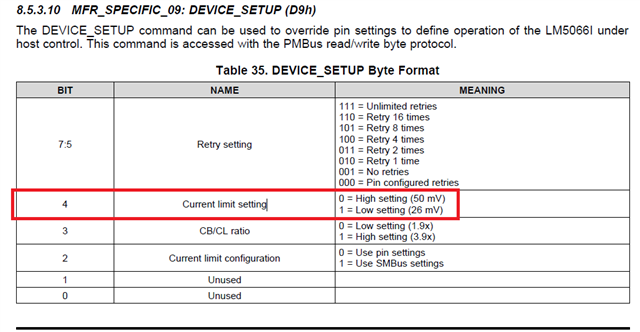

I would like to ask, what should Register DEVICE_SETUP (0xD9) be set to? Should bit4 be set to 0?

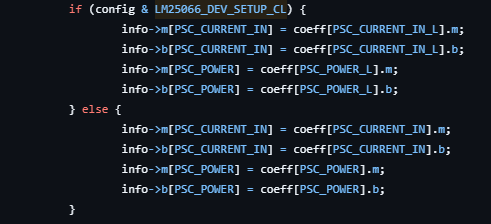

However, in the OpenBMC drivers/hwmon/pmbus/lm25066.c, when LM25066_DEV_SETUP_CL = 0 (bit4 Current Limit Setting), it uses the PSC_CURRENT_IN value.

From the lm5066i array, PSC_CURRENT_IN has m=15076; b=-504; R=-2, but this is inconsistent with what's shown in the datasheet. Instead, setting Register DEVICE_SETUP bit4 to 1 (26 mV) and using PSC_CURRENT_IN_L parameters would be consistent with the datasheet.

So I'd like to ask what Register DEVICE_SETUP (0xD9) should be set to? Why is the driver code inconsistent with the datasheet? Is there something wrong with my understanding? Please help explain.