Tool/software:

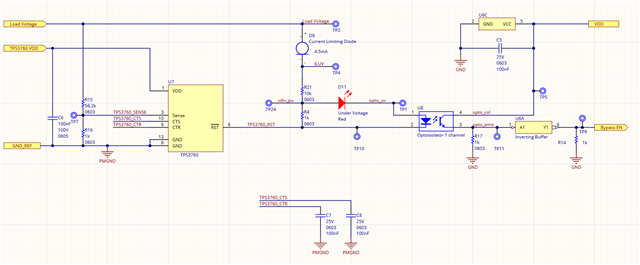

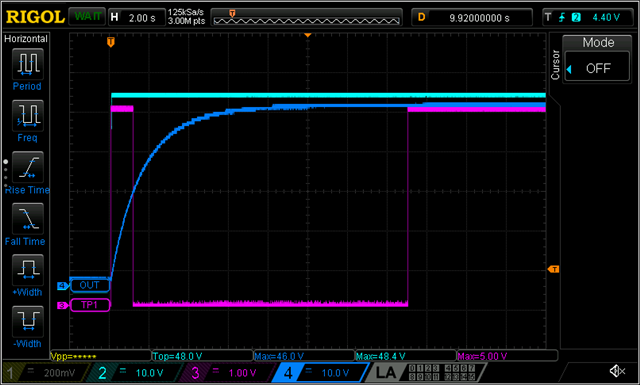

I'm using the TPS3760 to monitor for under-voltage conditions, specifically at startup. In my circuit during power-up, RESET is pulled high for about 1 second before going low until the UV sense condition is met.

Is there a way to hold RESET low at startup? I've tried different capacitances on CTR, but no change is observed.

In the screen capture below, CH2 is VDD, CH3 is RESET output, and CH4 is the voltage from which SENSE is monitored.

Is this behavior expected?

Thanks,

Matt