Tool/software:

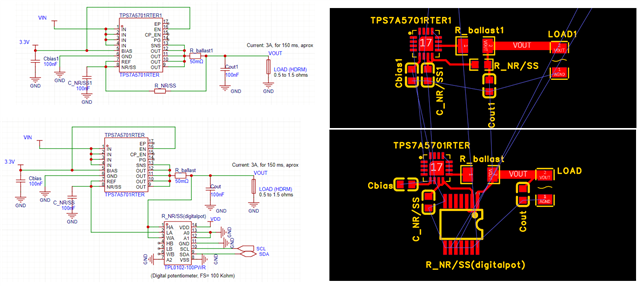

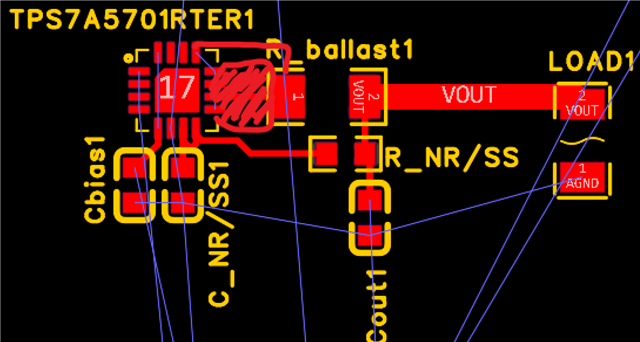

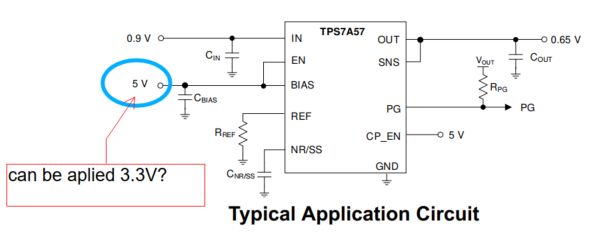

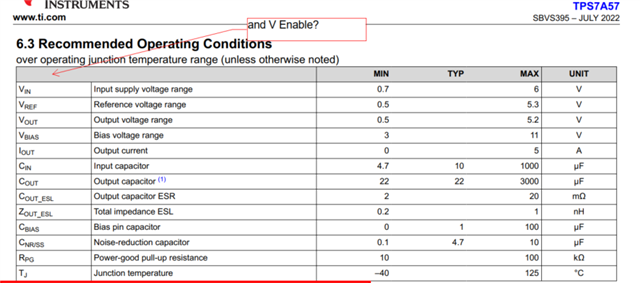

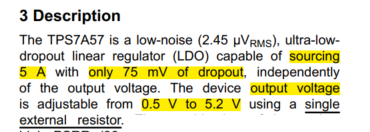

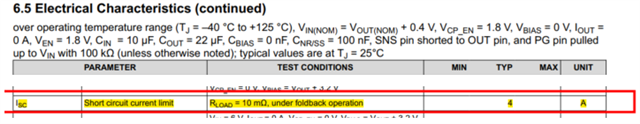

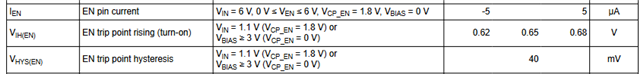

Hello, good afternoon. How to connect a TPS7A57 as a current source for a very specific application. My load has low resistance (between 0.5 ohms and 1.5 ohms) and I want to apply a direct current of 3 amps to it. If I do the math, the output voltage will be between (V=R*I) 1.5 volts and 4.5 volts, so I understand the regulator's input voltage will be those values plus the dropout value of 75mV, or 1.575V to 4.575V. My idea is to regulate the input voltage so that heat dissipation in the regulator is minimal. My question then is how to convert this voltage regulator to a constant current source. I need this current to be present for only approximately 150 ms and then turn off, which I plan to do by controlling the Enable pin. Thank you very much.