Tool/software:

Hello,

I am looking at using two TPS274C65BS devices in a SPI daisy chain with 24bit mode. I understand, the connection of the DSPI pin as well as the SPI connection between the devices and the master.

However I am not exactly clear on how the data transfer from the devices (slaves) to the master happens.

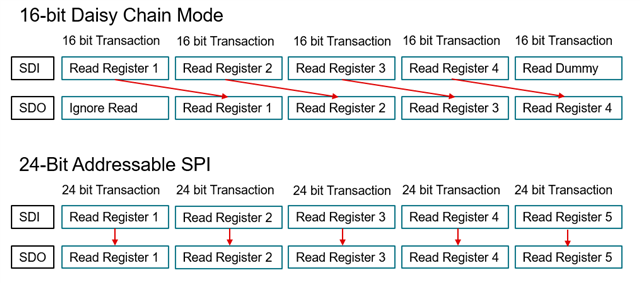

From the datasheet, it looks like the TPS274C65BS normally sends it data out (or response) simultaneously (or in the same 24bit cycle) as the data is received (the command) from the master. I.e. Figure 8-13 in the datasheet for a read.

However, in a daisy chain the TPS274C65BS has to shift the data received on the SDI pin to the SDO to be transferred to the next device. Therefore it cannot sent its data (or response) at the same time.

Does the TPS274C65 send its response on the next clock cycles?

Which means that for a daisy chain of two TPS274C65 devices in 24 bit mode, the first 48 clock cycles are used to send the commands to the two devices and another 48clock cycles are needed to receive the responses from the slaves (96clock cycles in total)? Or are 3x24 clock cycles required to get all the responses?

Maybe a more detailed diagram of two read commands (and responses) of two devices in 24bit daisy chain mode would be helpful.

Many Thanks & Best Regards,

Guillaume