Tool/software:

We currently hope to develop a fast power on/off function. PMIC is TPS65931211RWERQ1, SOC is AM62A74AUMSIAMBRQ1

At present, our motherboard will have a supercapacitor EDLC to maintain chip power supply for a period of time during power outages, facilitating the normal shutdown of various modules of the product and releasing resources. The following is the circuit schematic of the supercapacitor part

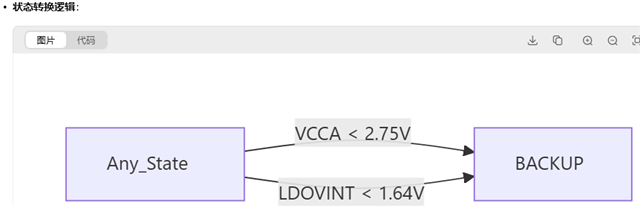

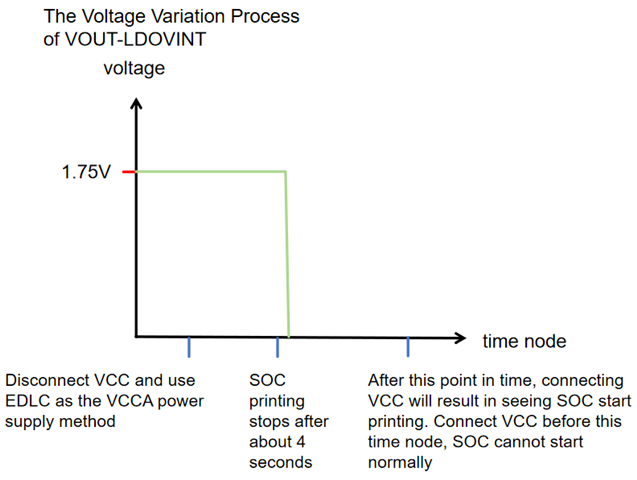

After disconnecting VCC (chip power supply), the supercapacitor begins to discharge for PMIC operation. At this time, when VCC is connected to curve1, SOC cannot start normally.

We need to wait until the supercapacitor discharges to curve2 before connecting VCC to start SOC normally.

The discharge curve of the supercapacitor is shown in the following figure:

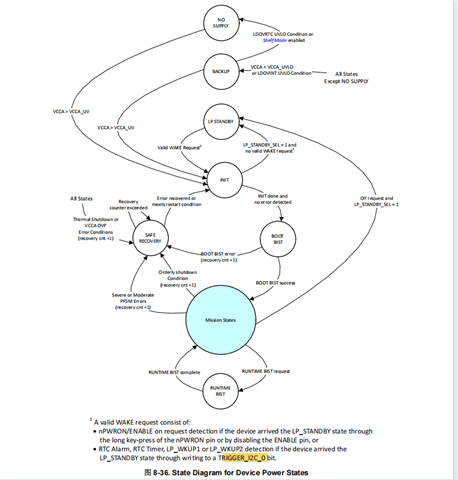

We speculate that PMIC needs a power-off process to achieve reset or normal shutdown, so that it can work properly when connected to VCC and powered on again.

In order to achieve fast power on/off function, we hope to manually control the normal shutdown/reset process of PMIC. Therefore, we would like to know which GPIO or register can be controlled to achieve the normal shutdown/reset operation of PMIC?

P.S.

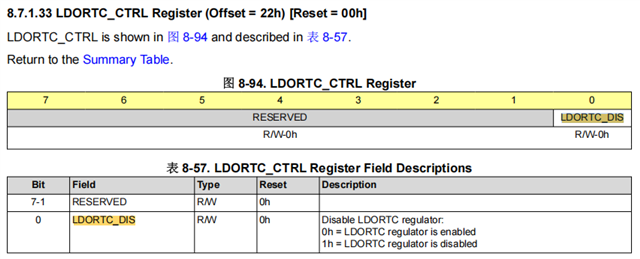

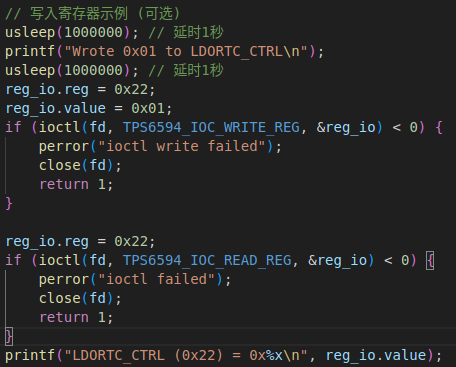

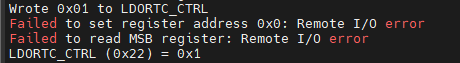

I have tried configuring the SOFT_REBOOT_REGIST of PMIC and writing 0x01 into this register to achieve the software reset operation of PMIC.

But it seems to have no effect. During the discharge process of the supercapacitor, resetting the PMIC, reconnecting VCC for power supply, and SOC also failed to start normally

So I want to know if there are any other registers that can make PMIC shut down/stop working normally