Tool/software:

Hello,

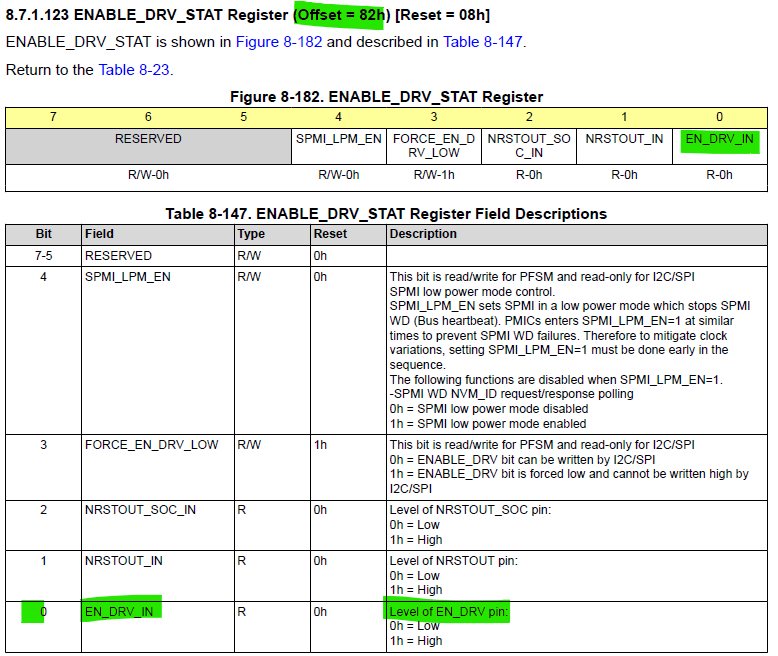

I am using TPS6594-Q1. I want to read the pin EN_DRV.

Current trying to read this register after initializing the PMIC WD(WD is activated, configured window1, window2 and long window times).

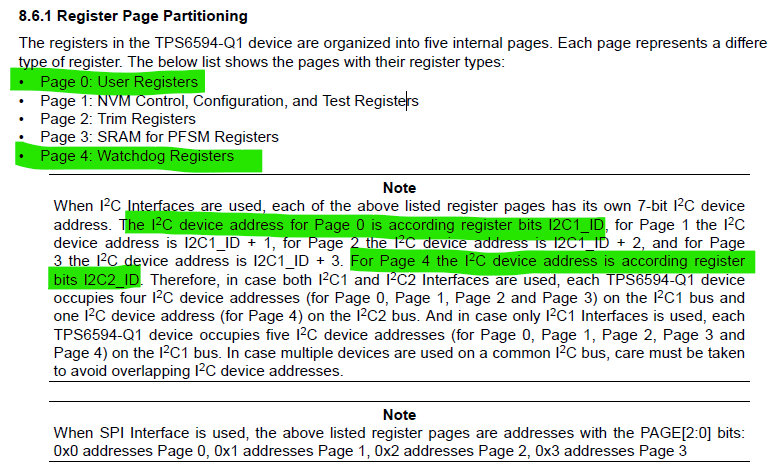

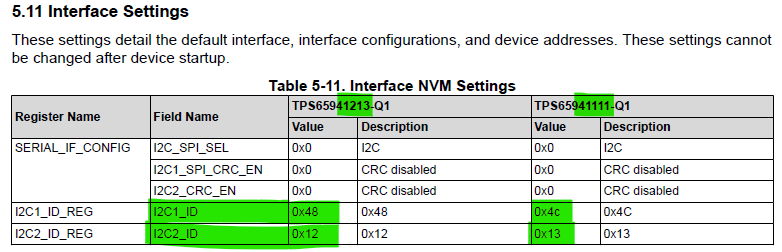

How can I read this pin? what should be the slave address if I want to read this pin. Which register has to be read to read the status of this pin?

note: I am using I2C bus to read PMIC register

Kind regards

Thanks