Other Parts Discussed in Thread: TPS62816-Q1

Tool/software:

Hi teams,

When TPS62813-Q1/TPS62816-Q1 run in the forced PWM mode during light load, is it stable or not?

Many thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi teams,

When TPS62813-Q1/TPS62816-Q1 run in the forced PWM mode during light load, is it stable or not?

Many thanks!

Hi Farheen,

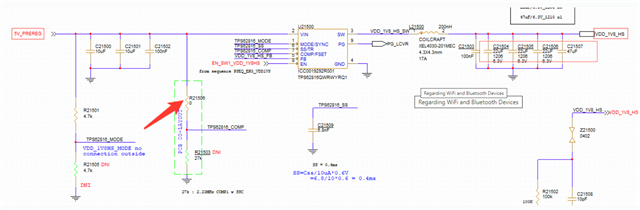

The mode pin is connected to Vin through a 4.7k resistor, it is work in FPWM mode.

My questions is 'is TPS62813-Q1 stable during light load ? '

The TPS62813-Q1 is based on a peak current mode control topology that is unstable during light load except add the dummy load or skip pulse, but I can't find any description about it.

Looking forward to your reply.

...

Hello Jiantan,

Sorry I am not able to understand the issue. Device is stable under light load in FPWM mode according to validation data.

Have you noticed something else?

Thanks,

Farheen

Hi Farheen,

The output of the TPS62813-Q1 with voltage drop during power on in very low probability(1/2000 times).

another question ---TPS62816-Q1

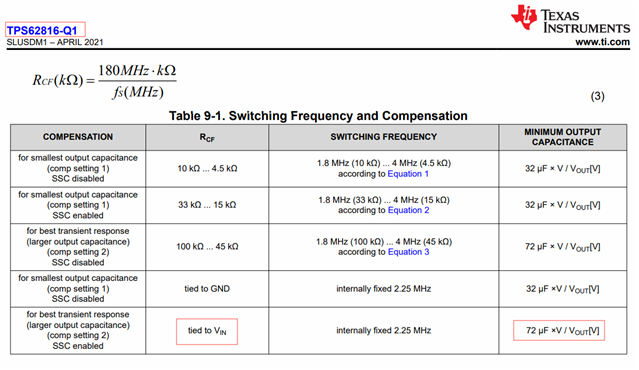

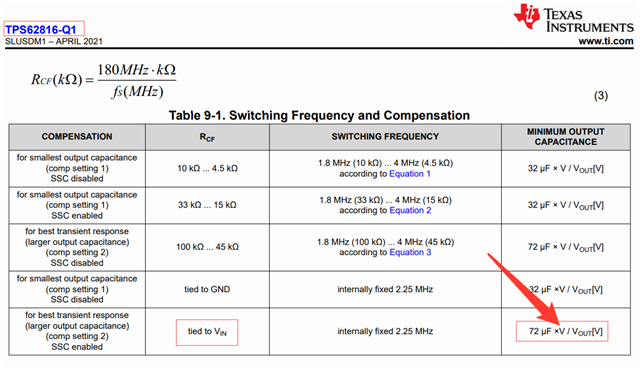

1.The COMP/FSET pin is connect to Vin, but the Vout is 110uF(datasheet recommend 200). is there any risk?

2.SCH

Please add your comment!

Hello Jianyan,

For TPS62813-Q1

How much is the voltage drop? Do you have measurement data and schematic?

For TPS62816-Q1

D/S recommends output capacitance of 72uF/Vout if COMP/FSET is connected to VIN, so for Vout 1.8V, it should be minimum of 40uF. Then it looks fine.

Thanks,

Farheen

Hi Farheen,

For TPS62813-Q1

It occur in very low probability, I don't have measurement data ,but the monitor chip detect it.

For TPS62816-Q1

What's meaning of 'V' in the datasheet as below , is it represent the Vin or the voltage unit?

Many thanks!

Hello Jianyan,

The "V" in the equation is part of the unit 72uFxV. It is not VIN.

Thanks,

Farheen