Tool/software:

Hi Team,

when the device output is short, PG gets low. However, after the short condition has gone, still PG is low.

What kind of condition, PG get recover to High? such as ADJ off to on

Best,

Shoo

Tool/software:

Hi Team,

when the device output is short, PG gets low. However, after the short condition has gone, still PG is low.

What kind of condition, PG get recover to High? such as ADJ off to on

Best,

Shoo

Hi Shoo,

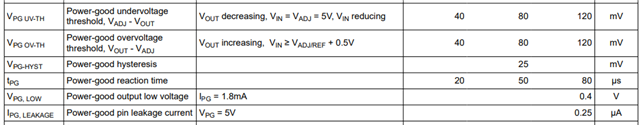

PG is based on a comparator between the out pin and the ADJ pin. Power-good should recover to high within 80us after VOUT reaches within 40mV of VADJ to remain within spec, see V_PG UV-TH and t_PG parameters from the Electrical Characteristics table.

Does PG stay low even after it returns to regulation for a period of time?

Does it stay low after power cycling?

Best,

Gregory Thompson

Hi Gregory,

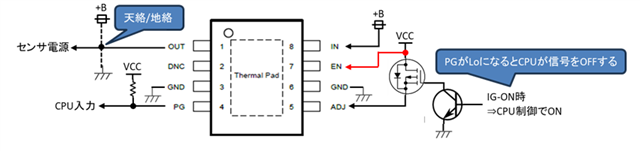

The background is that they changed TLE4254EJS to TPS7B4261 and TLE4254EJS doesn't have independent EN pin. so kind of different operation.

They connect to EN to VCC to return the regulation. but when ADJ is off, The PG goes low.. This is because VADJ < VEN,OFF?

Best,

SHoo

Hi Shoo,

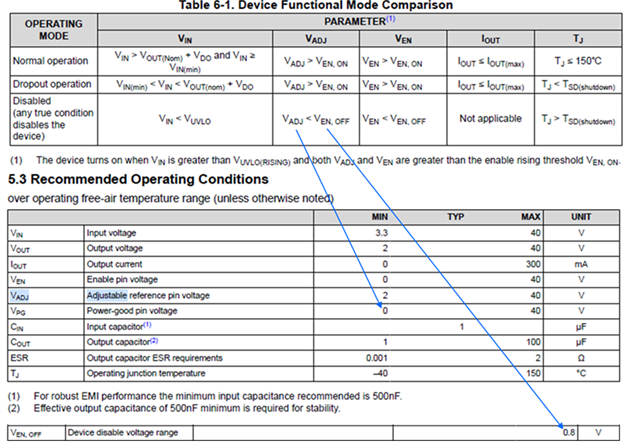

PG shouldn't pull up when the device is disabled, so yes this is likely because VADJ < VEN,OFF when low.

Does pull high again once you raise VADJ above that threshold?

Best,

Gregory Thompson

Hi Gregory,

yes, pull high again. So the reason is VADJ < VEN,OFF. Could you please show the difference between TPS7B4261 and TLE4254EJS ?

I heard they are drop-in replacement.... but PG and status pin behavior is kind of diffreent.

Best,

Shoo

Hi Shoo,

VADJ < VEN,OFF is the reason why PG would stay low, I agree.

The PG and ST pin behavior of the TPS7B4261 and the TLE4254EJS is the same within the Recommended Operating Conditions and Functional Range, respectively, so we consider it a valid drop-in replacement.

The TPS7B4261's PG pin should not pull high if the device is in the disabled mode (UVLO is triggered, VEN<VEN,OFF, or VADJ<VEN,OFF, etc).

The TLE4254EJS doesn't have a secondary EN pin, this should be responsible to the difference between the chips.

I haven't tested a TLE4254EJS in the lab but if ST is pulling high when the ADJ/EN pin is low enough to disable the device, this is indeed a difference between the parts that is not explicitly defined by either datasheet.

Best,

Gregory Thompson