Other Parts Discussed in Thread: ISO5852S

Tool/software:

Hello experts:

we have some questions regarding the design calculation Excel sheet "UCC1524x-Q1_Calculator_V8 (*1)."

We apologize for the many questions, but we would appreciate it if you could respond.

Best regards,

Zhou

[Assumptions]

* Input Voltage: 24V

* Output Voltage: 18 V/-2 V (Dual output)

* Application: Power device driving gate driver power supply

[Questions]

- Understanding of Input Cells and Output Cells

I understand that the user inputs values in the green cells, and the output appears in the white cells. Is my understanding correct that filling in all the green cells completes the design (circuit constants only)?

- Regarding C_OUT1B on line 48, and C_OUT2 and C_OUT3 on lines 51 and 53 2-1) Can I assume that the calculation results on lines 48, 50, and 52 in the Excel sheet represent the minimum required capacitance, and it is acceptable to select components with larger capacitance?

2-2) Is my understanding correct that we are seeking the minimum value of the black line in Figure 12-5 of the datasheet (*2)?

2-3) It seems that changing the Max. component tolerance values inputted on lines 25 to 29 of the Excel sheet does not affect the calculation results on lines 48, 50, and 52. Does this mean that these results do not include tolerance, and we need to consider tolerance when selecting actual capacitor components?

2-4) I believe that for C_OUT2(MIN) and C_OUT3(MIN), we need to select capacitors with capacitance larger than these values. However, if we select a capacitor that exceeds the calculated capacitance due to a -20% tolerance, and the actual capacitance is +20%, would that result in a total capacitance of +40% compared to the calculated result still be acceptable?

2-5) As mentioned earlier, since the calculation results for COUT2 and COUT3 are marked with (MIN), selecting components with capacitance larger than the calculated results will change the ratio of COUT2 to COUT3. Is that a problem?

2-6) The datasheet Table 12-2 states, "The COUT2 and COUT3 capacitance ratio is important to optimize the dual output voltage divider accuracy." Is there a method to calculate the output voltage variation? For example, if we select capacitors with capacitance larger than the results on lines 50 and 52, the ratio of COUT2 to COUT3 will change from the calculated results. How can we calculate the impact on the output voltage?

- Regarding the currents from lines 17 to 20

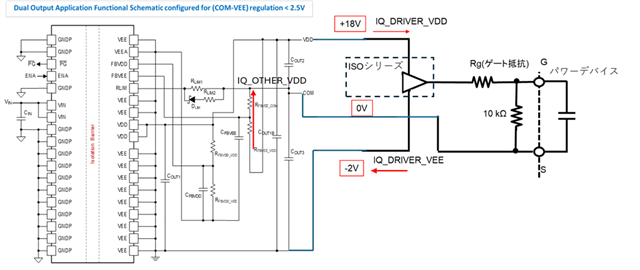

I recognize the meanings of each variable as shown in the attached image, is that correct? If I am mistaken, I would appreciate your guidance on those points.

* IQ_DRIVER_VDD and IQ_DRIVER_VEE: Current consumption on the gate driver circuit side (excluding the switching current flowing through Rg in the attached image and the current flowing through 10kΩ)

(Example: When using ISO5852S, IQ_DRIVER_VDD = IQ_DRIVER_VEE = ISO5852S's Output-supply quiescent current (max) 6mA)

* IQ_OTHER_VDD: Current flowing through RFBVDD_VEE and RFBVDD_VDD

* IQ_OTHER_VEE: None (0A)

- Regarding RFBVDD_VEE and RFBVEE_VDD on lines 23 and 24 As stated on page 38 of the datasheet, is it acceptable for RFBVDD_VEE=10k and RFBVEE_COM=10k to remain constant at 10kΩ regardless of design values such as output voltage? I understand this is for the filter formed with the 330pF capacitor. In this design, since the voltage between VEE and COM will be less than 2.5V, I plan to adjust the resistance value on line 24 to bring RFBVEE_COM closer to 10kΩ.

- Regarding the determination of power input values on lines 37 and 39 I could not find the SOA curve (*2) corresponding to the desired output voltage of 18V/-2V in the datasheet. If there is an SOA curve for 18V/-2V, could you please provide it? If you cannot provide the SOA curve for 18V/-2V, could you suggest an alternative design method (e.g., using the SOA curve values for 18V/-5V)?

- Regarding the impact of power input values on the design on lines 37 and 39

* If the value on line 37 is small, the cells from lines 13 to 20 turn red. How should this be interpreted?

* If the value on line 39 is small, how do the values on lines 48 to 52 change, and what calculations are being performed?

*1 Design calculation Excel sheet: https://www.ti.com/tool/download/UCC15241-Q1-CALC [https://www.ti.com/tool/download/UCC15241-Q1-CALC]

*2 Datasheet: https://www.ti.com/lit/ds/slusf14/slusf14.pdf?ts=1756166123483 [https://www.ti.com/lit/ds/slusf14/slusf14.pdf?ts=1756166123483]

*3 Evaluation board: https://www.ti.com/lit/ug/sluucj2c/sluucj2c.pdf?ts=1756097715366&ref_url=https%3A%2F%2Fwww.ti.com%2Ftool%2Fja-jp%2FUCC14240EVM-052 [https://www.ti.com/lit/ug/sluucj2c/sluucj2c.pdf?ts=1756097715366&ref_url=https%3A%2F%2Fwww.ti.com%2Ftool%2Fja-jp%2FUCC14240EVM-052