Tool/software:

Hi,

We are currently evaluating the TPS1H100AQPWPRQ1 for our design and are conducting a fault mode analysis according to IEC61010-1 (Clause 4.4.1, single fault condition).

From the datasheet and functional safety documents, we understand that pin-to-pin short is listed as a potential failure mode.

In particular, we would like to confirm the following point regarding our safety evaluation:

https://www.ti.com/jp/lit/fs/slvaej7/slvaej7.pdf

-

Question:

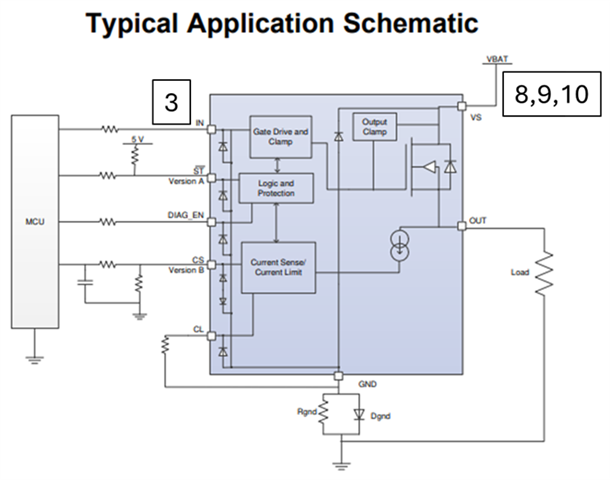

Is it possible that pin 3 (IN) and pin 8/9/10 (VS) could become shorted internally as a result of a single fault?

If so, should we consider this fault mode as part of the IEC61010-1 single fault condition testing?

-

Background:

-

IN pin is rated for 0–5 V operation (abs. max. −0.3 to 7 V),

-

VS is specified up to 40 V (48 V load dump for 400 ms).

Therefore, an internal short between IN and VS would apply voltages beyond the IN pin’s maximum rating and could propagate high voltage to the MCU.

We would like to clarify whether TI recommends assuming this short as a credible failure mode in safety analysis.

-

Your guidance on whether this specific fault (IN–VS short) should be explicitly included in IEC61010-1 SFC testing will be highly appreciated.

Best regards,

Conor