Tool/software:

Hello,

i am using the TPS6508640 to power my PCBA with AMD Kintex FPGA.

What I notice is that the PMIC restarts its sequence when enabled for 10...100 times (hiccupping) before reaching a state that its sequence is done.

When I readout the I2C registers I get at register 0x05 value 0x01 and at register 0xB4 value 0x13. This means that some sections of the die have reached critical temperature and an emergency shutdown is triggered.

After clearing the bits by writing 1 the values are set back to 00 when I read back the register. Then I start the power down sequence and again the power up sequence. And again the Critical temp bits are set.

I cannot imagine there is realty an over temperature as it only takes 10...12ms between retries.

The first step of the sequence is buck2 for 0V85. It enables PG on GPO1 and this continues the chain/sequence.

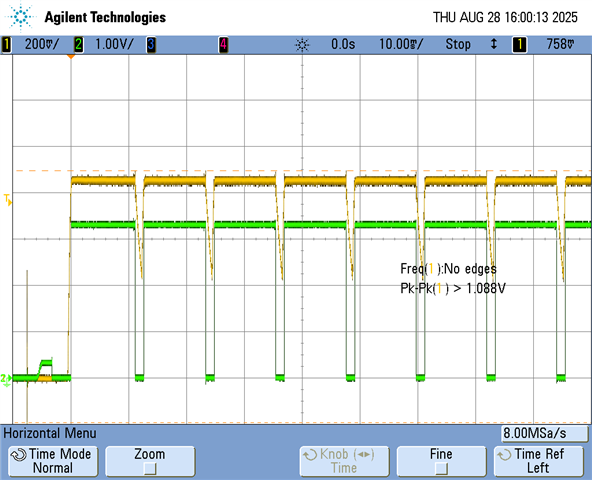

In the oscilloscope picture yellow is the 0V85 rail of buck2 and green the GPO1 PG_buck2.

By looking at the other PG signal on GPO4 I noticed that GPO1 and GPO4 are going low at the exact same moment and this guided me to an emergency shutdown. And the registers confirmed that it was indeed triggered.

But... why?