Tool/software:

How to validate the PSRR of LDO in this PMIC.

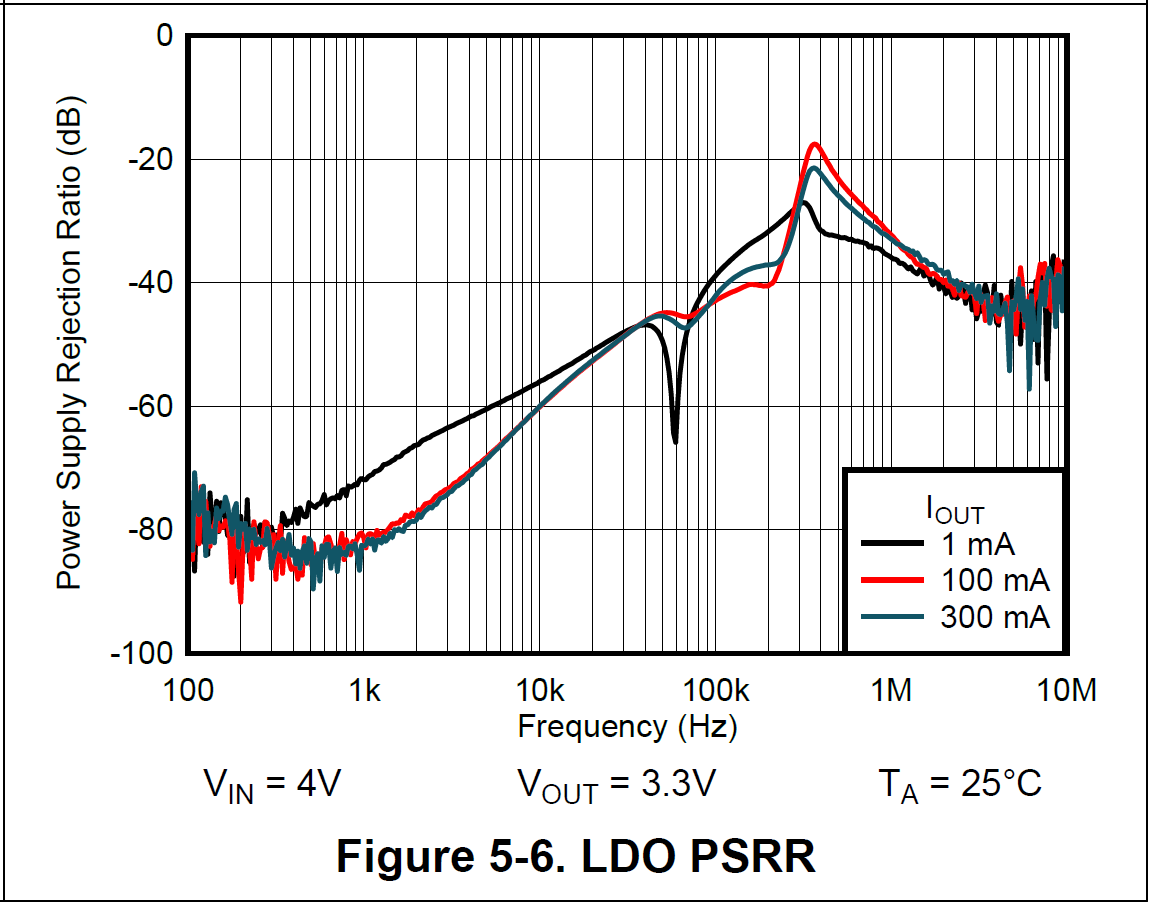

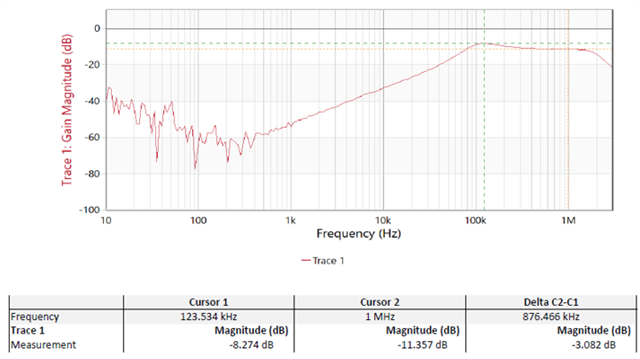

You have mentioned high LDO PSRR which is <-18dB approx. in the datasheet.

I have tried out the following procedure:

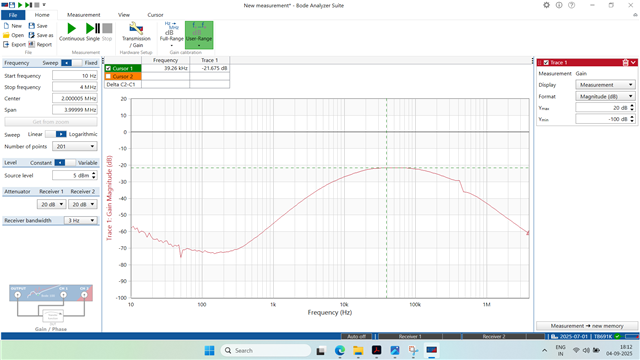

Scenario 1:

unlock

02 DD 91 #unlock the control registers

05 AA B8 #unlock the configuration registers

04 1A B4

sequence elimination

0D 3F F2

0E 3F CD

0F 3F D8

10 3F 4C

11 3F 59

03 1d ca - 4V Off

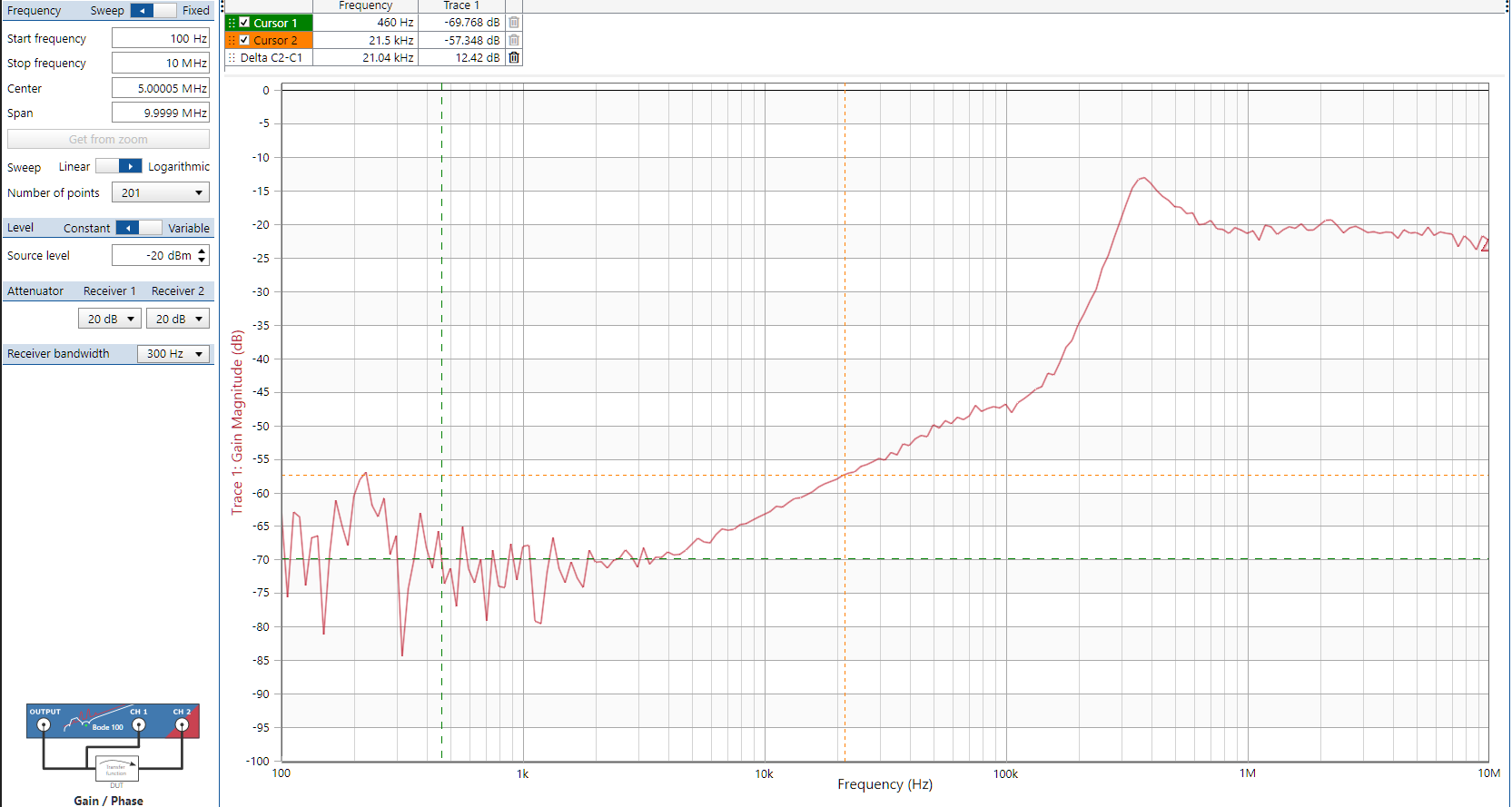

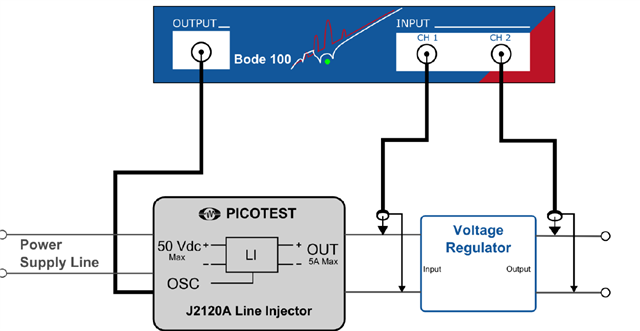

Connect Bode 100 as per the below circuit and gave ext supply as 4Vin to LDO via Line injector.

No output at LDO as NRST is low.

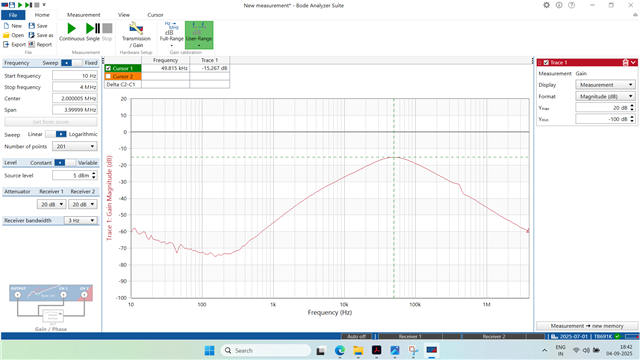

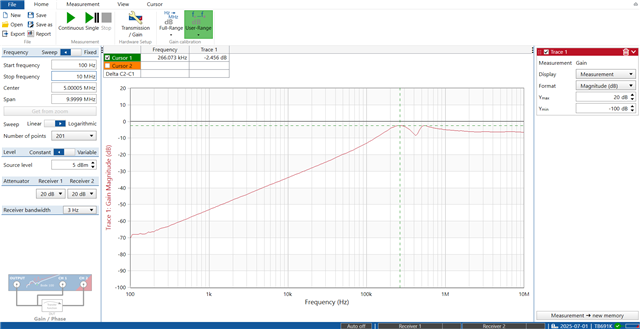

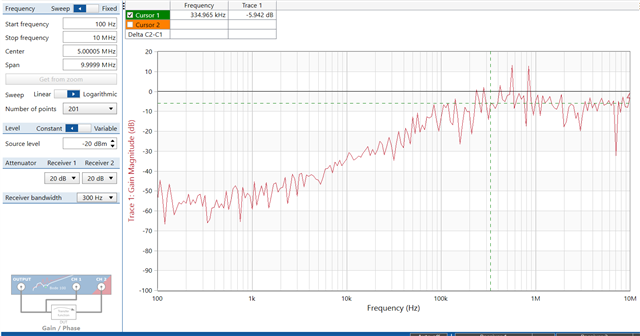

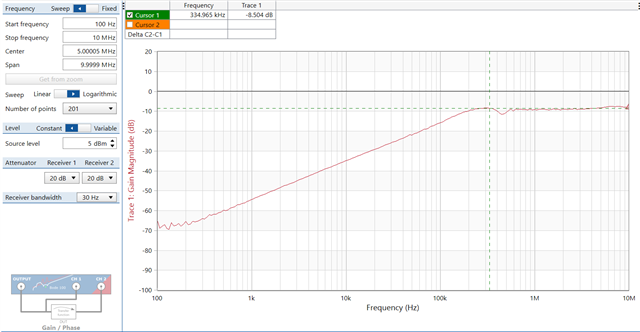

Scenario 2: Gave external voltage to LDO output in addition to scenario 1.

Is the procedure followed correctly?

Are we missing any commands?

What will be the passing criteria for LDO PSRR? (Vin:4V, Vout:3V3)

Kindly guide us.