Other Parts Discussed in Thread: LMZM33606

Tool/software:

Hi,

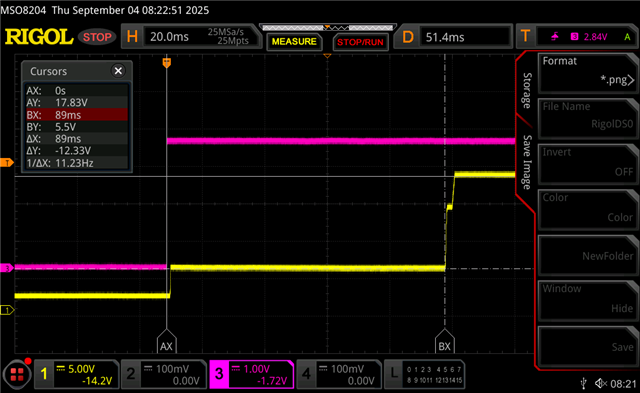

We are using the TPS611781RNWR in our design as per the below schematic snippet to generate 18V from a 12V rail. The EN is controlled from a GPIO. We have seen that there is a quite long delay from the EN going high to the TPS611781 starting up - about 90ms per the below measurement.

Is the EN -> startup time a constant and known number? I could not see it in the datasheet.

EN -> Output Measurement

Yellow trace (Ch1) is VCCp18V0 rail (output of TPS61178).

Pink trace (Ch3) is EN signal

The VCCp18V0 rail sits at about 2V when EN is low. When EN goes high, the VCCp18V0 rail goes to an intermediate 5.5V level. 89ms after the EN signal goes high, the TPS611781 appears to begin it's proper startup, which takes ~3ms to complete. The VCCp18V0 rail then reaches 18V.

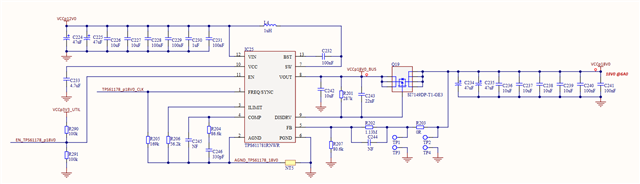

Schematic