Other Parts Discussed in Thread: SN74LVC1G08, LMG1020

Tool/software:

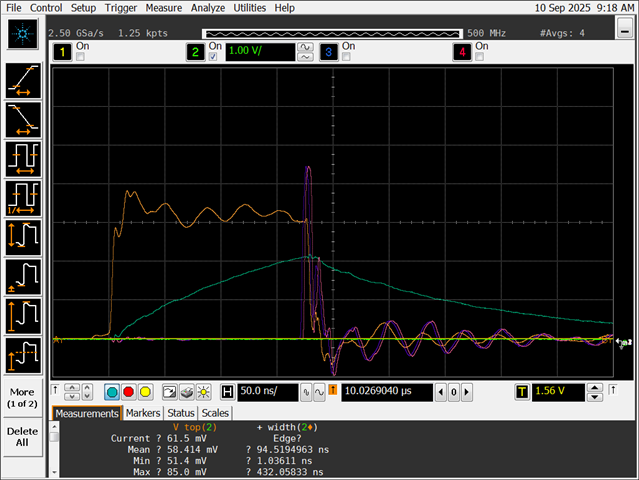

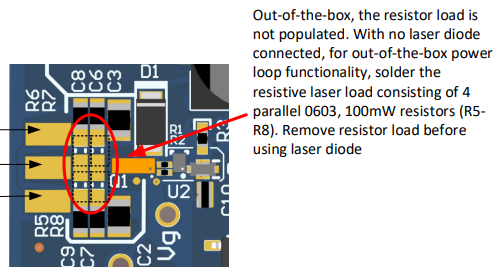

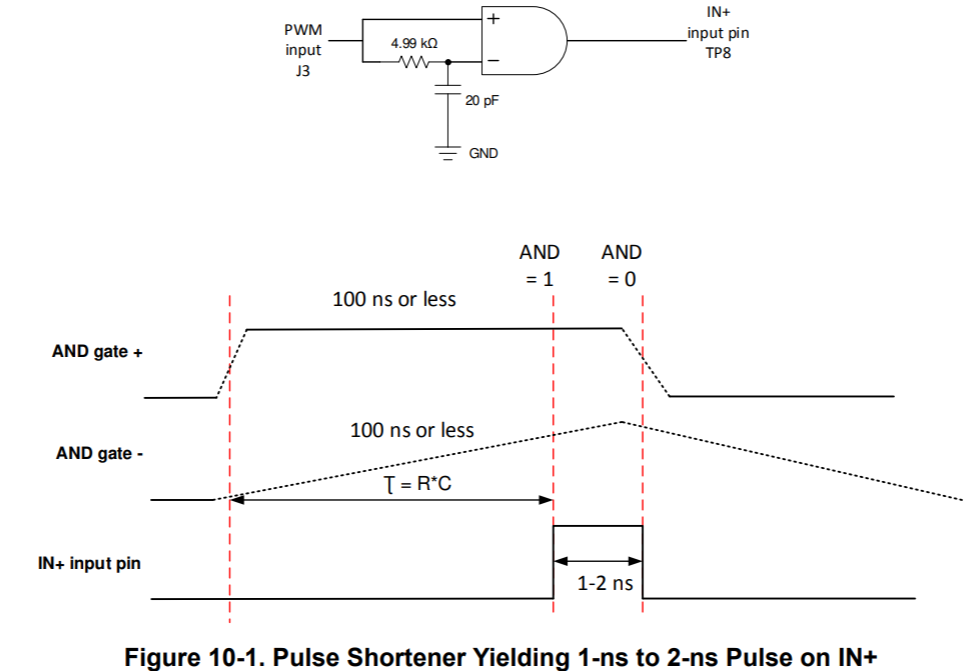

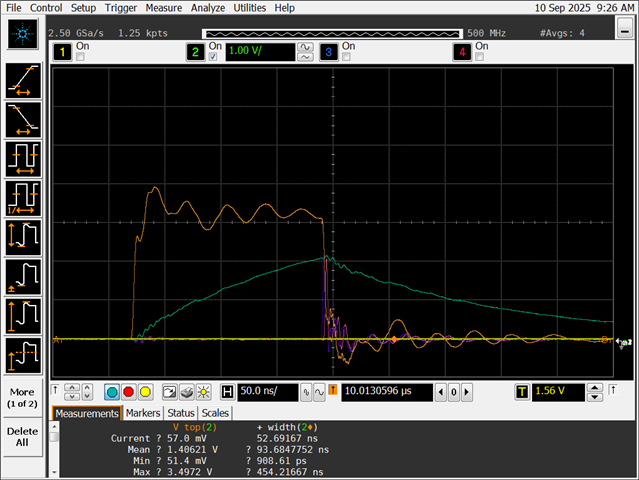

We use LMG1020EVM-006. This image is quoted from the EVM User's Guide: LMG1020EVM-006.We are adjusting the frequency of the function generator to achieve the narrowest possible pulse width (1 ns) at the output.

I would like to increase the output signal amplitude of the AND gate SN74LVC1G08 used in the LMG1020EVM-006 evaluation board.

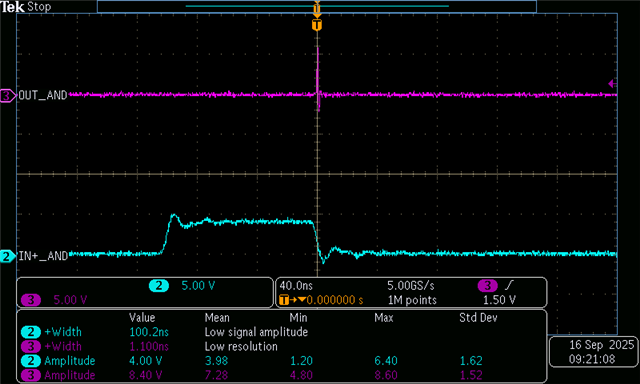

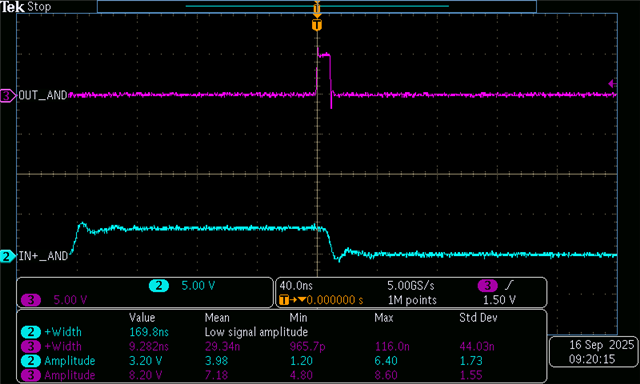

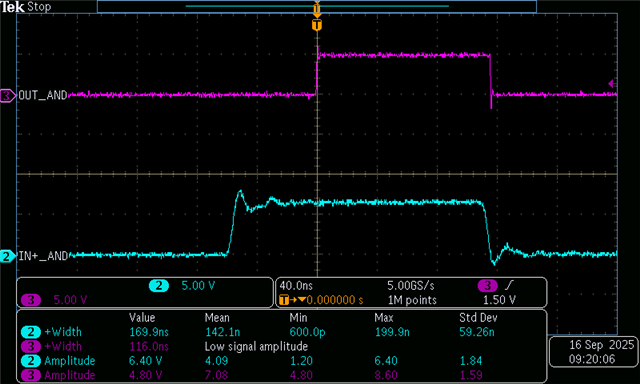

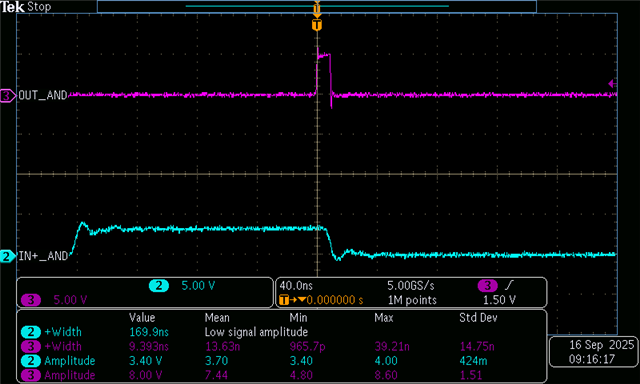

The reason is that when trying to generate narrower pulses from the SN74LVC1G08, we found that the signal amplitude decreases.

How can we maintain the output amplitude while still generating narrow pulses from the SN74LVC1G08?

[

[