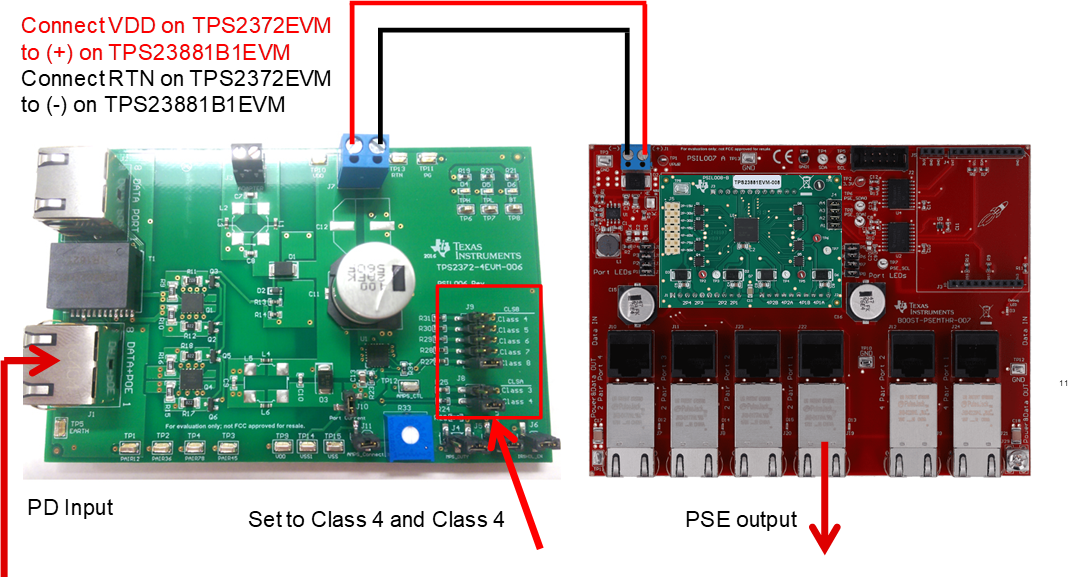

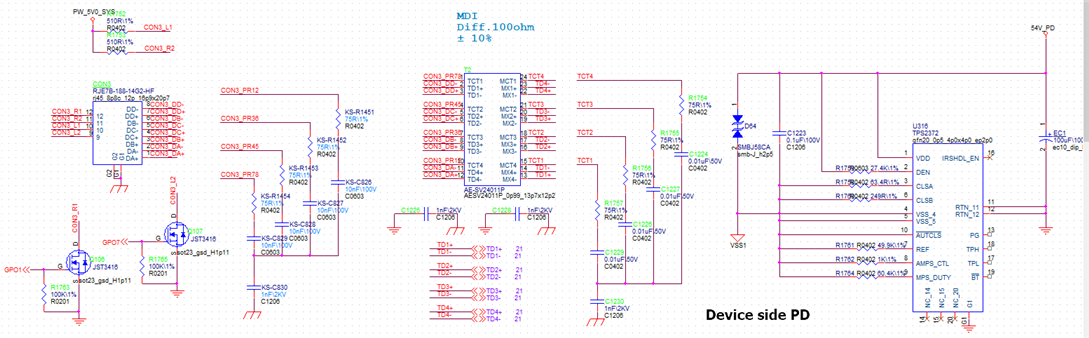

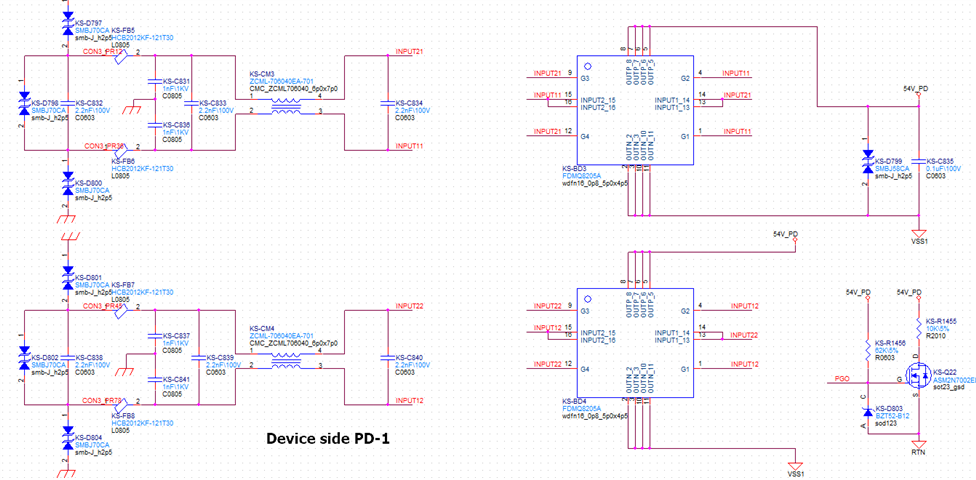

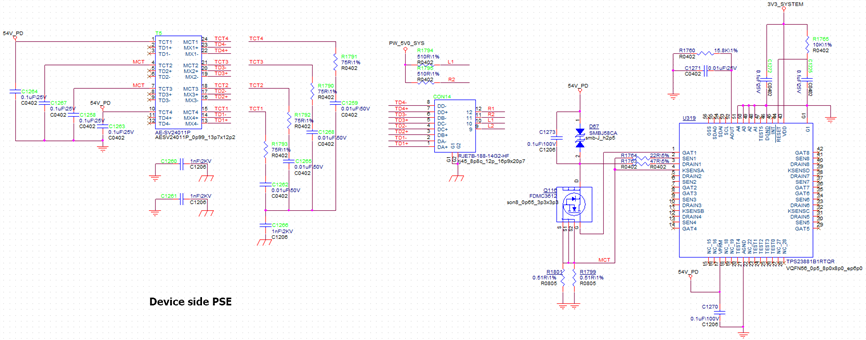

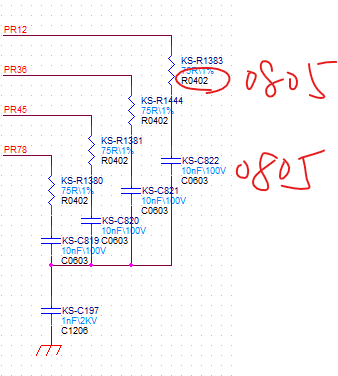

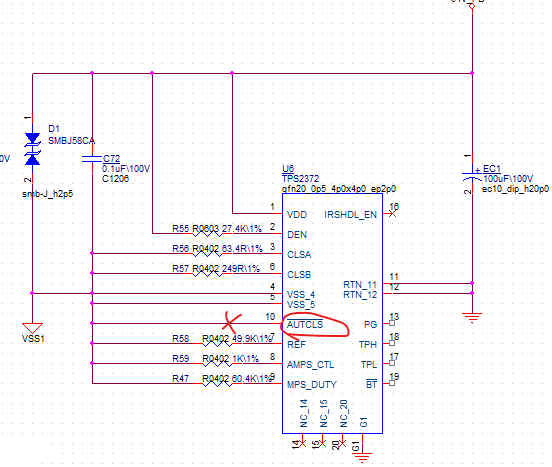

Other Parts Discussed in Thread: TPS23881, TPS2372, , TPS23881B, TPS23861, TPS2378

Tool/software:

Dear Madam/Sir,

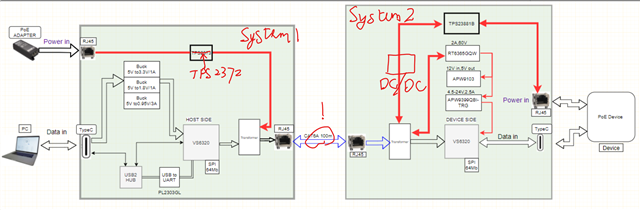

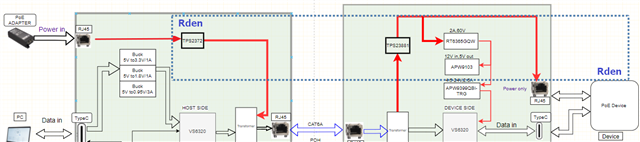

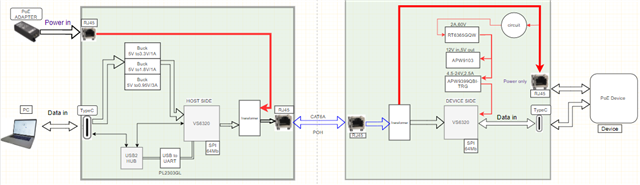

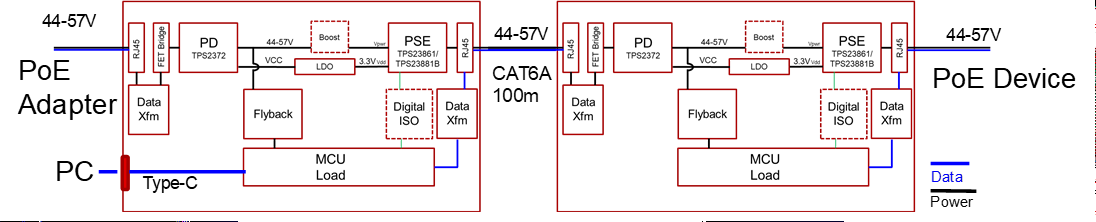

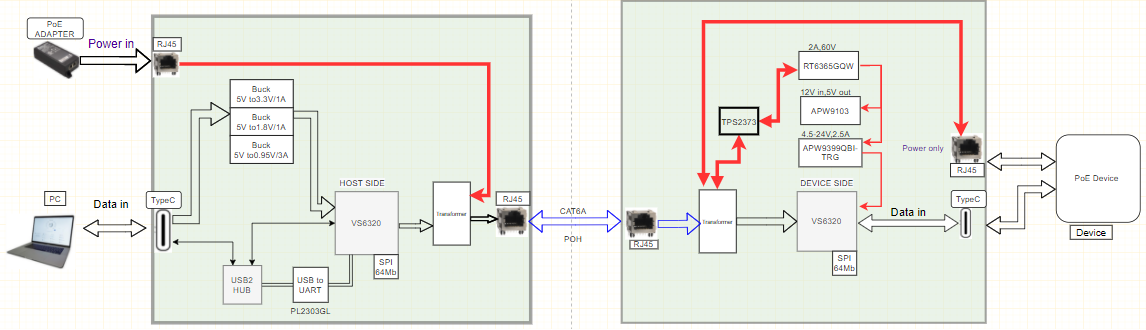

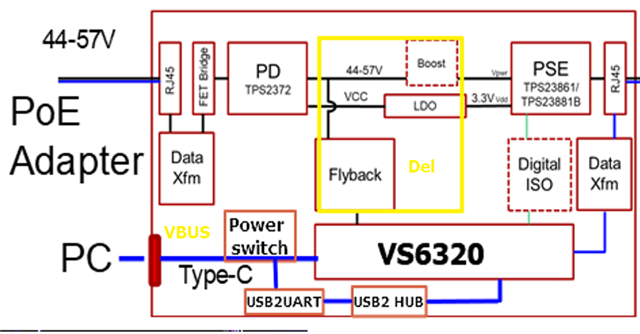

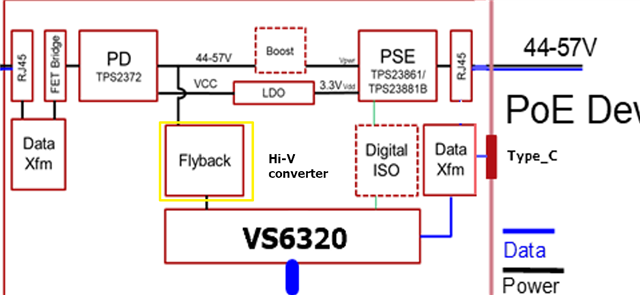

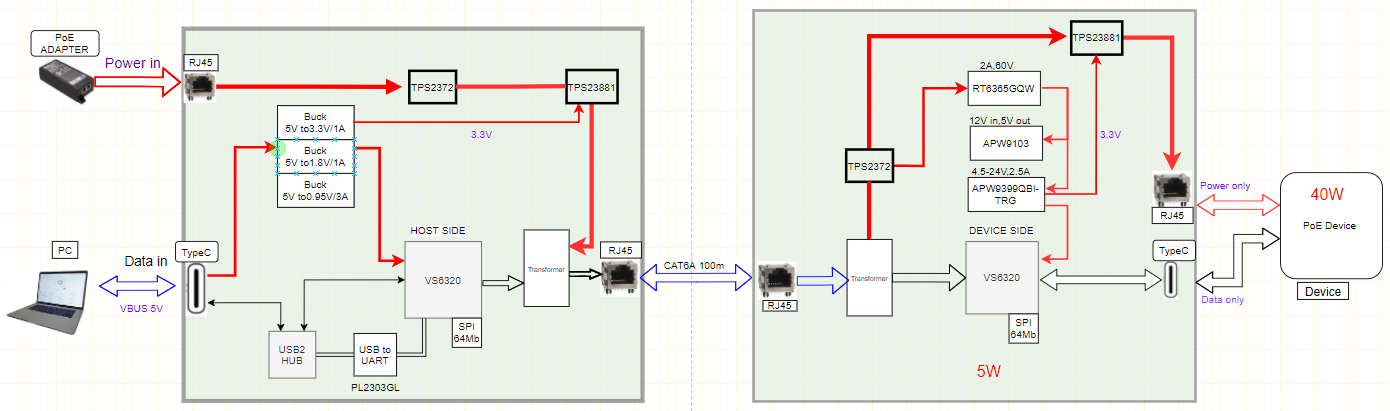

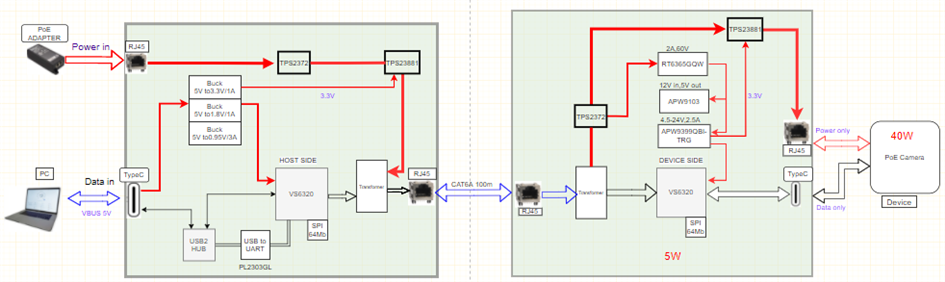

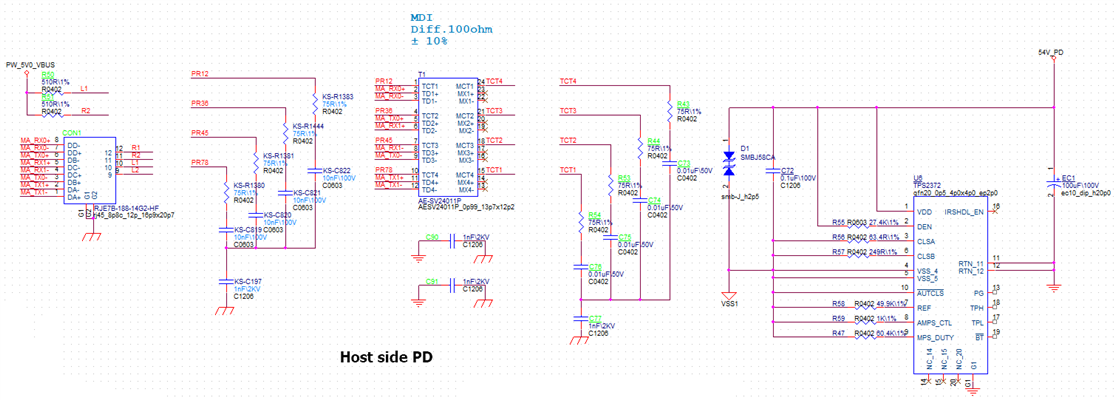

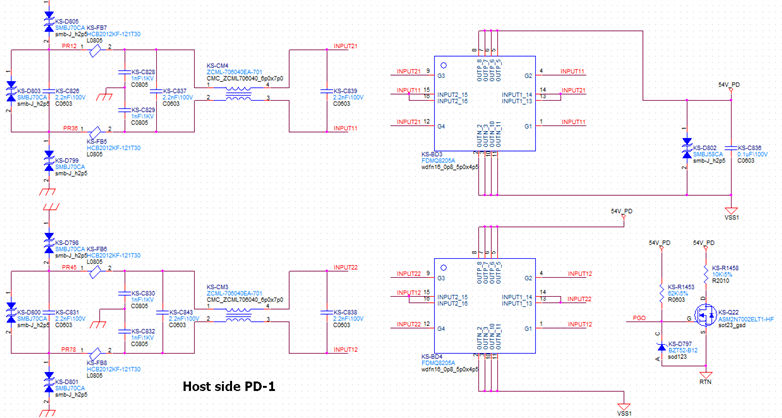

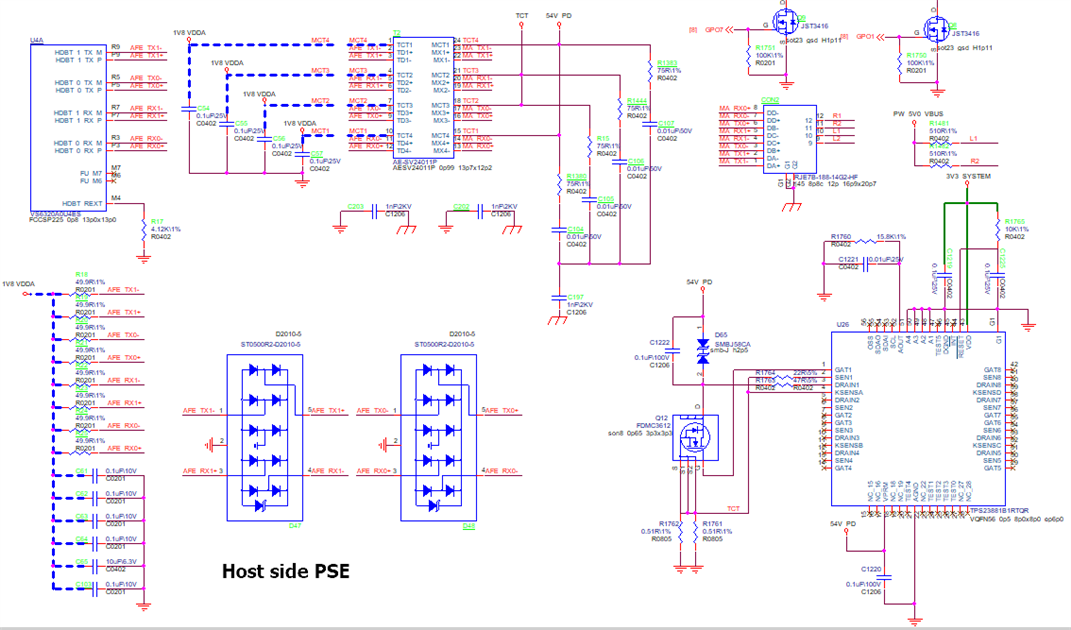

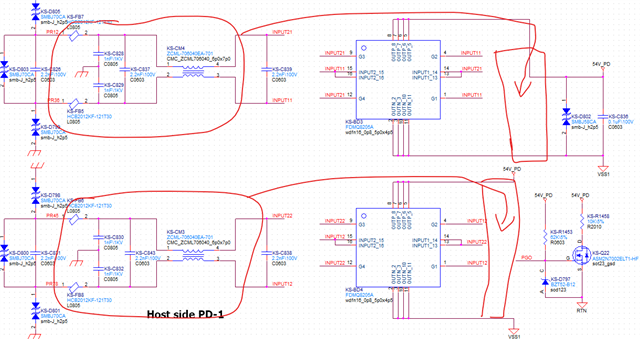

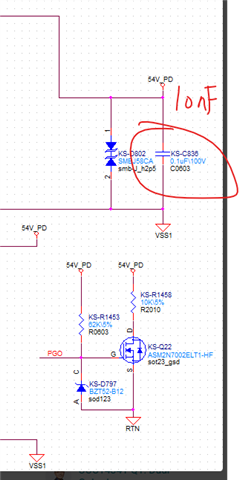

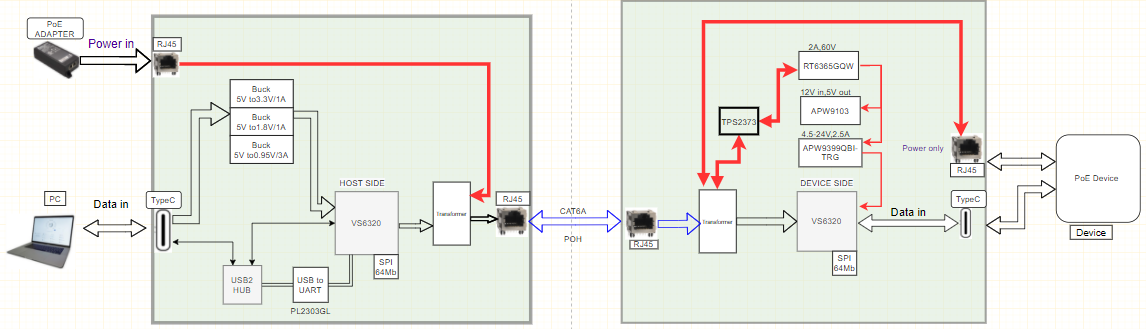

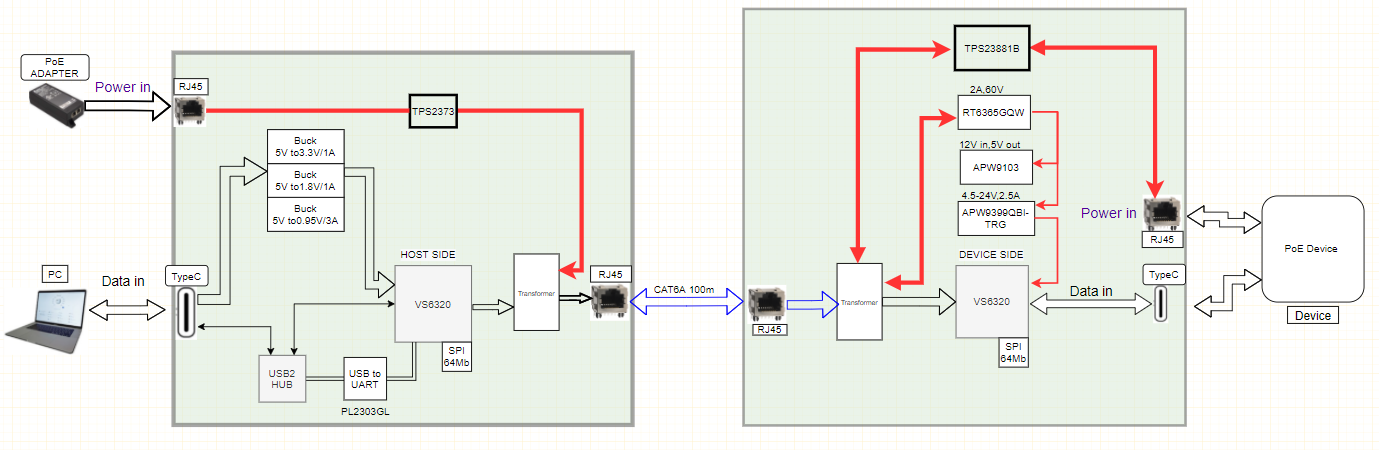

We'd like to build a system as follows.

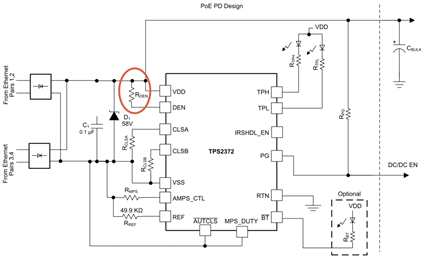

We have never used the dual-signature PD before, so we are not sure whether this architecture is workable or not.

Please give us some suggestions to complete this design.

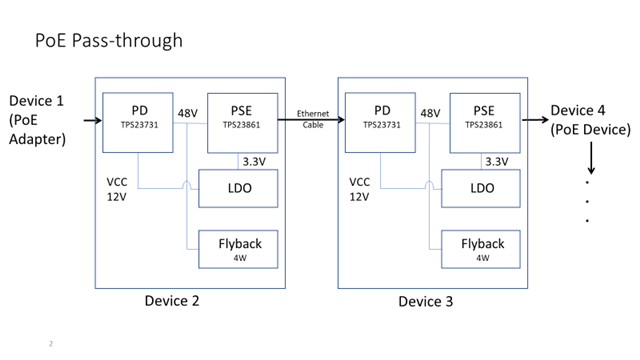

By the way, the customer provided an idea as follows:

They want to use a PoE adapter to provide power to the endpoint PoE camera.

PoE adapter → PD (pass-through) → PSE → PoE camera

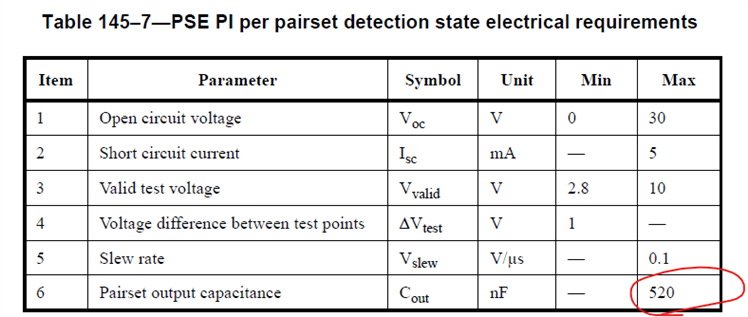

We think the PoE signature detection may fail.

Is the customer's idea workable or not?

thanks