Other Parts Discussed in Thread: BQSTUDIO

Tool/software:

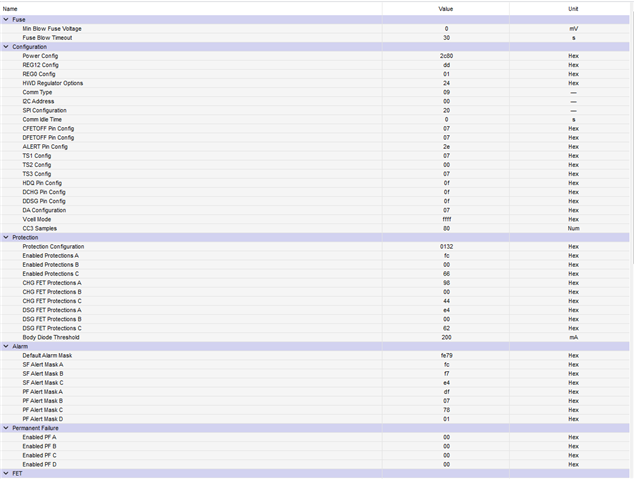

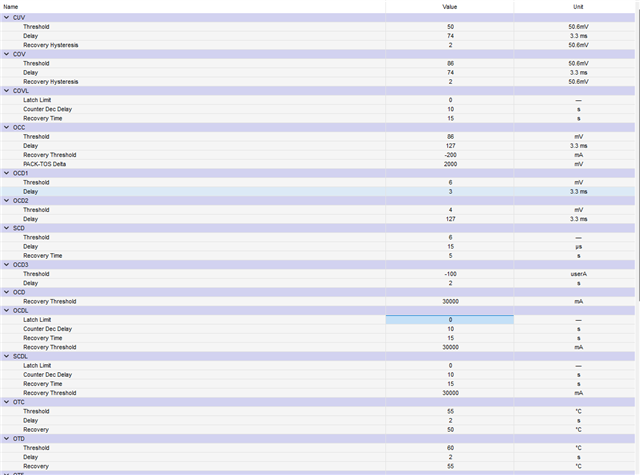

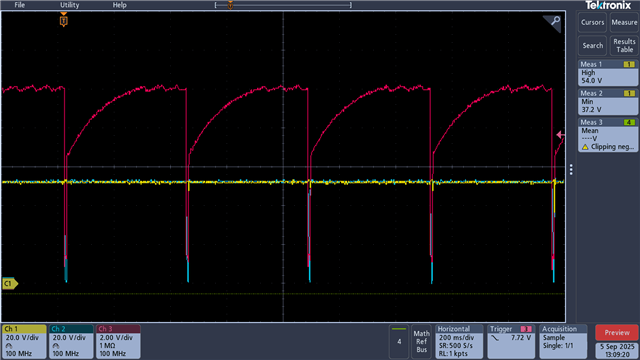

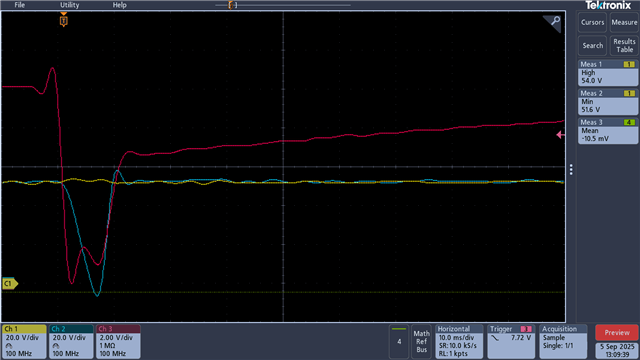

I am trying to test that the OCD1, 2, 3 and SCD functions correctly. Normally, our OCD thresholds will be in the hundreds of amps, but I am just trying to check basic functionality at lower currents. I've currently configured OCD2 to trigger at -48A. When I enable the load to pull 60A, I see OCD2 get triggered correctly in BQ-STUDIO, the DSG Vgs correctly is driven to 0V. It then is driven back on. OCD2 then triggers again, creating this oscillation.

I see OCD2 Alert get set in BQ-STUDIO, not OCD2 Status. Then OCD2 Alert clears (unsure if that related - just an observation).

I am just trying to have the DSG FET be disabled and stay off (including PDSG) after an OCD2.

Interestingly enough, when I use the command ALL FETS OFF, the response is as expected - all FETs remain off. I have successfully used ALL FETS OFF for 720A.

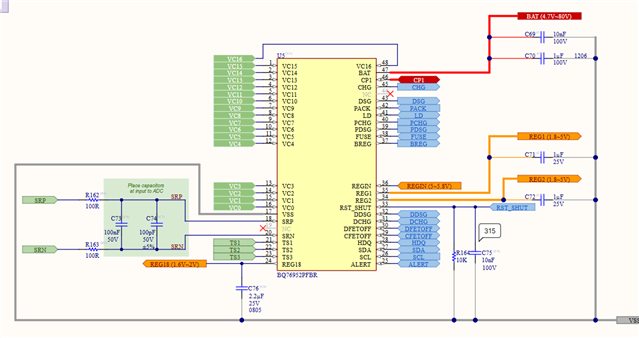

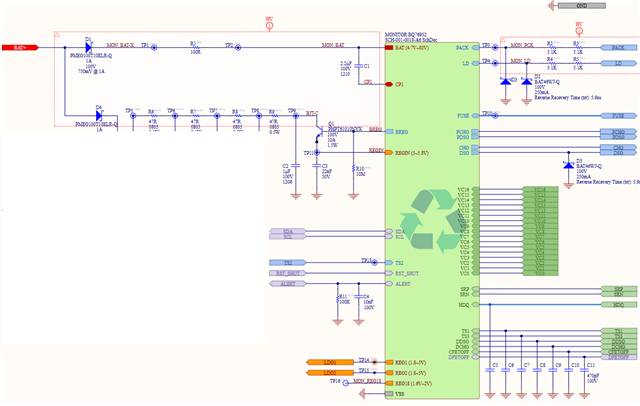

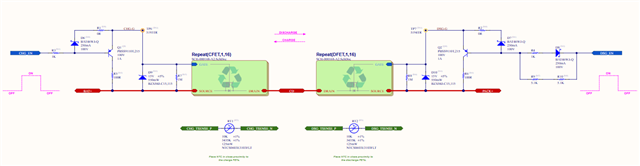

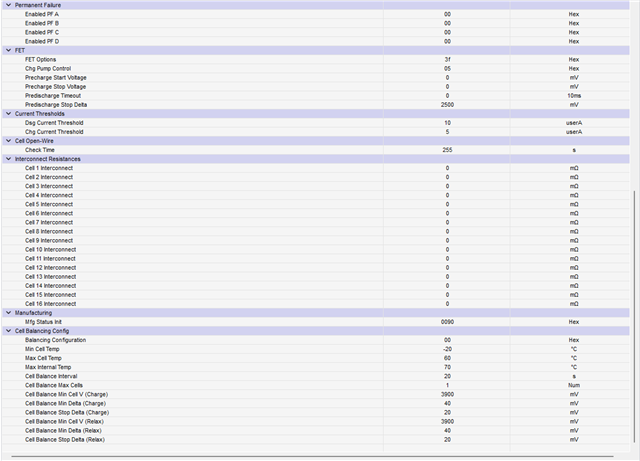

Below are what I believe to be the relevant settings, and the oscilloscope captures.

Red = DSG-VGS

Blue = PACK+