Tool/software:

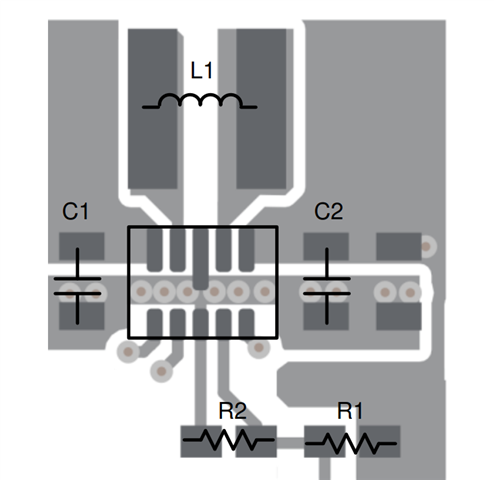

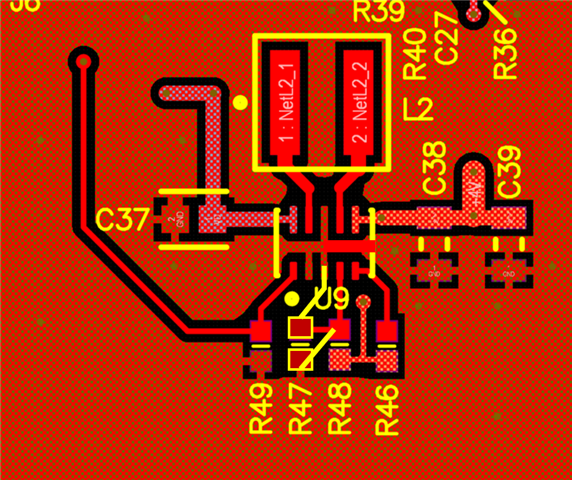

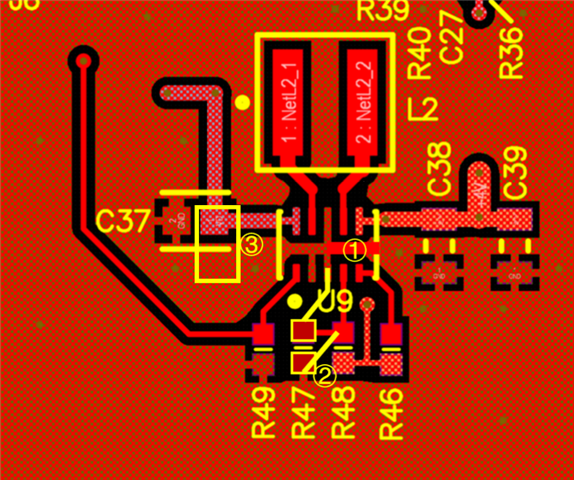

A regulator is built using TPS63802DLAR. It takes the power (VD on schematic) from a single Li-Ion cell and converts it to 4V. A typical load current is 300-500mA with very short bursts up to 1A. The enable signal is 0V/2.5V. About 1000 boards were built, and so far two parts failed after several months. Once failed, they take sink about 100mA from the power source even with the enable pin at 0V. The enable function still works, i.e. there is 4V on the output with enable pin high and 0V with enable low. I am attaching the schematic and the layout. The PCB has four layers with a massive ground pour on the top and bottom plus the ground plane with frequent vias, so the part doesn't get hot.

What can go wrong?