Tool/software:

In the loop compensation of the UC2854 IC, is there any relation between the loop compensation pin (Pin 7) and the PKLMT pin (Pin 2)? Specifically, is there any relation between the voltage loop compensation and the current limit?

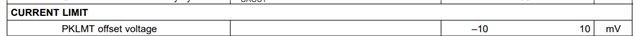

Also, please explain the concept of offset voltage in the PKLMT pin. How does it vary with the capacitor connected to it? For example, we observed an offset voltage of about 30 mV when using a 100 nF capacitor. Please provide any correlated data showing the variation of offset voltage with respect to different capacitor values in this IC. The datasheet specifies a range of –15 mV to +15 mV, but we are seeing different values depending on the capacitor used.