Tool/software:

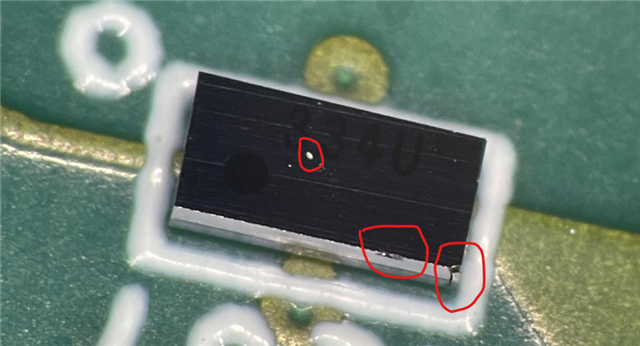

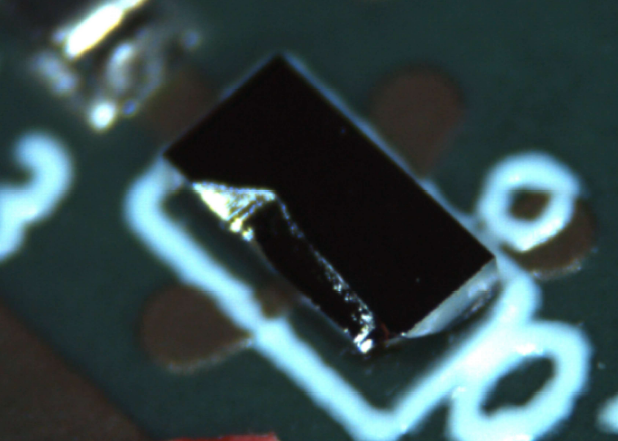

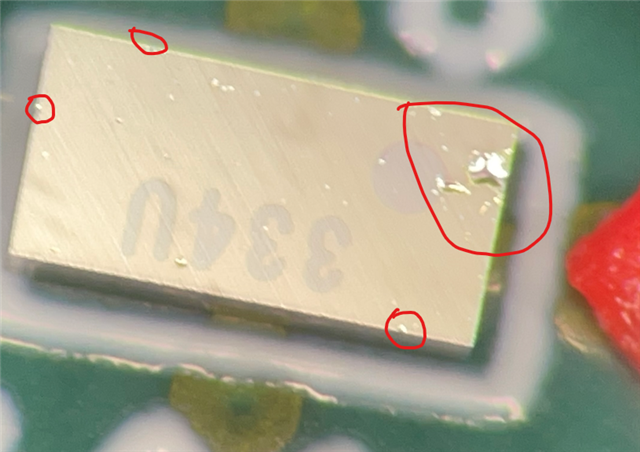

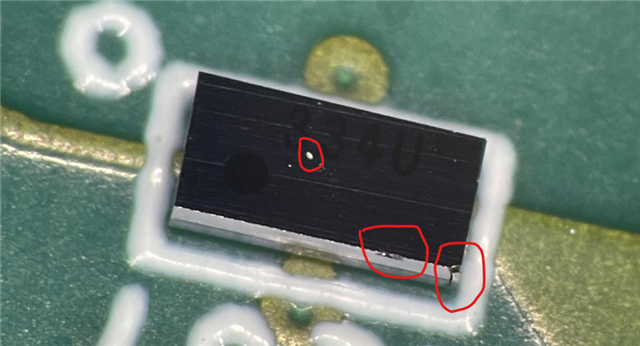

We are seeing a wide range of chip outs on the component body (post SMT processing) and we would like to under if there is an acceptability requirement.

Tool/software:

We are seeing a wide range of chip outs on the component body (post SMT processing) and we would like to under if there is an acceptability requirement.

Hello Bryan,

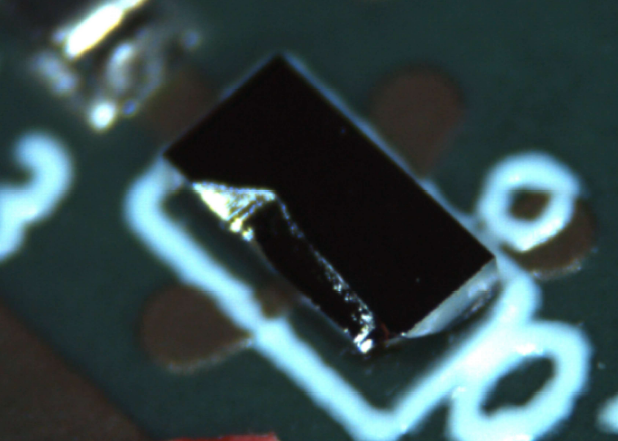

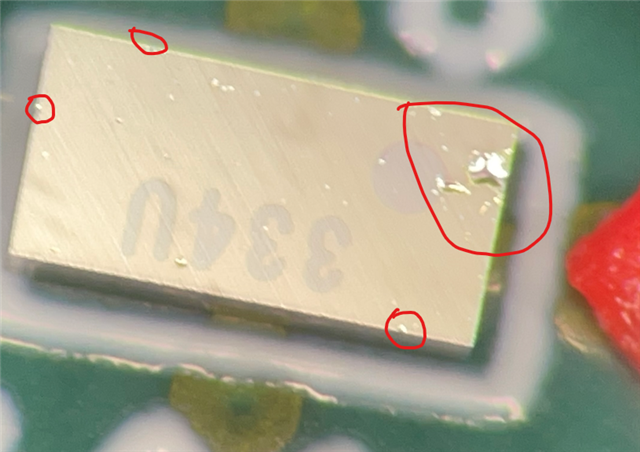

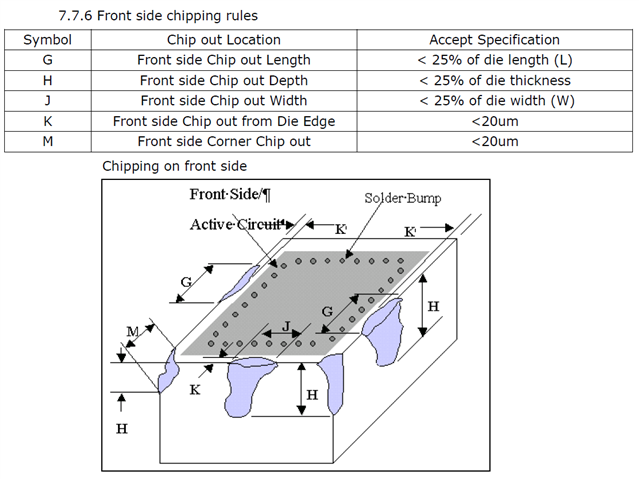

Thanks for your interest in TI FETs. Back side (marking side) chip-out depth should not exceed 25% of the die thickness and 50% of die length or width. Front side chipping rules are shown in the table and diagram below. The biggest concern for front side chipping is if the chip extends into the active area of the die. The small chipouts shown in 2 of the pictures are acceptable and would pass TI's optical inspection prior to tape and reel. The 3rd picture is not acceptable and would not pass TI's optical inspection. I'm including some useful links on TI's chip scale FETs below. These are essentially silicon die with solderable pads or BGA interconnect. They require care when handling and assembling onto a PCB. Please let me know if you have any questions.

FemtoFET SMT guide: https://www.ti.com/lit/ug/slra003d/slra003d.pdf

Solving assembly issues with chip scale power MOSFETs: https://www.ti.com/lit/an/slvafh0/slvafh0.pdf

WCSP handling guide: https://www.ti.com/lit/ml/sszqnf6/sszqnf6.pdf

WCSP/DSBGA application report: https://www.ti.com/lit/an/snva009ai/snva009ai.pdf

Best Regards,

John Wallace

TI FET Applications

Hi Bryan,

You're welcome. Glad I could be of assistance.

Best Regards,

John