Tool/software:

Hello,

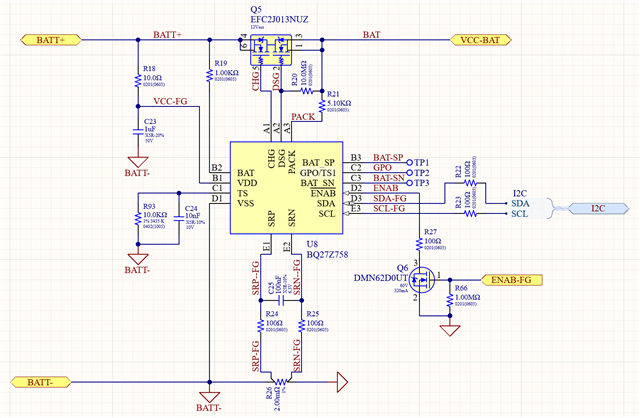

I am working with a BQ27Z758YAHR configured with two external NFETs EFC2J013NUZ (back-to-back, common-drain). The circuit is essentially the same as the reference schematic in the datasheet (around page 24).

Test conditions and observations

-

Battery: single cell, 3.95 V, 1500 mAh

-

PACK: powered from a bench supply set to 4.2 V, current limited (no load observed)

-

BAT_SP = 3.57 V, BAT_SN = 0.00 V

-

DSG = 3.74 V with PACK = 4.2 V → the gate is below PACK (so NFETs remain OFF)

-

CHG: not measured in this setup

-

VDD = 3.95 V, BAT = 3.95 V

-

ENAB = 3.57 V (also tried forcing it low, no improvement)

-

TS: ~8 ms pulses at ~612 mV (seems normal)

In these conditions, the external FETs remain OFF (PACK+ is isolated from BAT+).

I²C note

At the moment, I have not implemented I²C communication. The SDA and SCL lines are at 0 V (no pull-ups installed). I am wondering if the absence of I²C/pull-ups could itself prevent the FETs from being enabled, or if I²C is only required to read/clear possible latched faults.

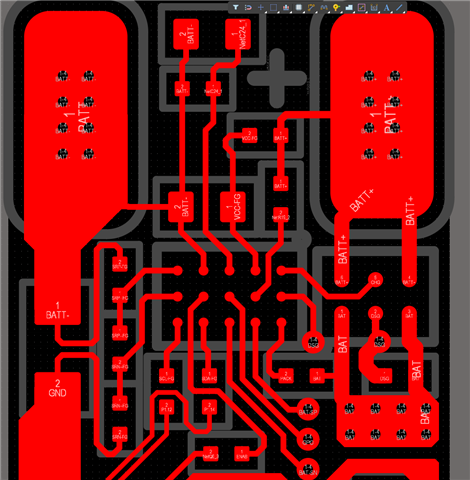

I am attaching the schematic and layout in case I have overlooked something.

Thank you for any suggestions!

— Giulio Montanari