Tool/software:

Hello,

I am working on 500W PFC design using the UCC28070EVM. I recalculated component values using the Set-up Tool SLUC114 Rev 2.0 and applied these changes to the EVM. The boost inductors are MnZn (example Wurth 74437429203151) as recommended by TI some years ago when I was working on a similar design.

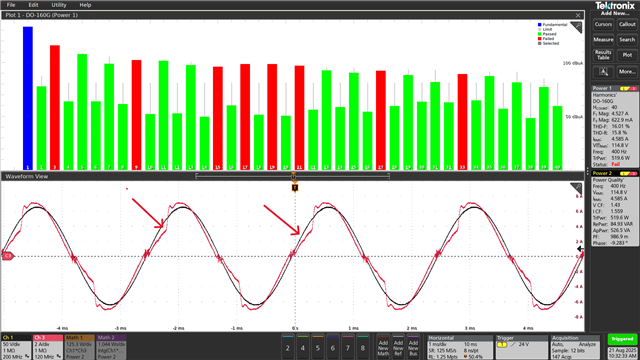

The results of the component changes to the EVM revealed input current distortion, as shown in the image below, that I was unable to overcome with adjustments to the component values. The current distortion causes non-compliance with the DO-160G Current Distortion requirement.

Is the cause of this current distortion a circuit set-up issue?

It appears to be a specific condition that causes the distortion, since it occurs after the zero crossing.

The attached zip file contains the Ver 2.0 Set-up tool with my design inputs and with the component values used to set up the circuit that produced the waveform in the image below.

Please review and let me know if I can provide further information.