Tool/software:

Thanks for reaching out. I have a few questions to help narrow this down:

- Is there a consistent bus state when I2C is locked? Is SDA low while SCL is high? Is SCL stuck low?

- [Reply]In some cases its only one line that sticks low but it can have both lines stuck low as shown

- When you tried bit banging SCL, did you also generate a STOP (SDA rising while SCL is high) after 8 to 16 clocks?

- [Reply]The recovery sequence 9 bits and a stop

- Are the interruptions on SDA and SCL intentional (for testing) or naturally occurring in your system?

- [Reply]naturally at first, but can be replicated easily by momentarily grounding sda or scl. We have a battery on the I2C lines that can momentarily disconnect (due to drop etc) similar to the hot insertion explained in the application note.

- Could you share scope captures (showing SCL and SDA) of the stuck condition and a normal transaction for comparison?

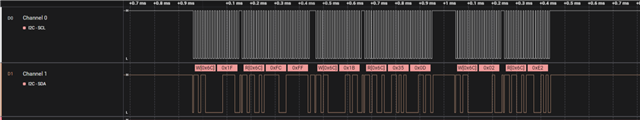

- [Reply]Normal transaction

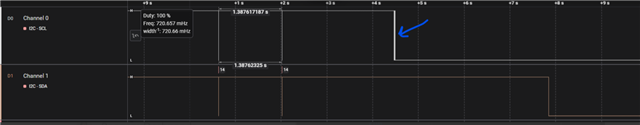

- Interruption

- attempted recovery

I agree that resetting the device isn't ideal. Once we understand what the bus is doing when it gets stuck, we can work on a better way to recover and prevent it from happening.