Other Parts Discussed in Thread: TL431

Tool/software:

Hi TI team,

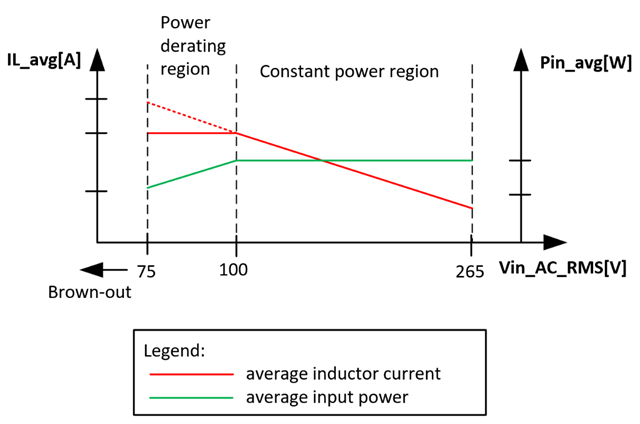

I have a question about analog boost PFC controller IC "UCC28180". I want to implement a power derating for the line voltage values below 100VAC (rms). In case of Vin < 100VAC_rms, i want to limit the average current (and hence the input power of PFC). If it is possible I want to force the current loop to limit the average current through the inductor to a fixed value. if the load tries to draw more current, then the output voltage drops under its set value.

Figure 1: aimed power derating behaviour

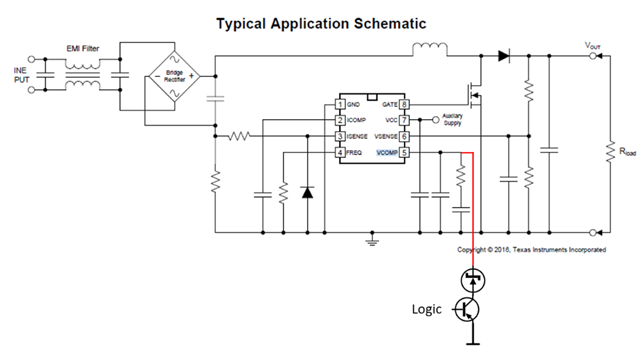

As you can see in figure 1, in normal case the current will looks like the dotted line (between input voltage range 75-100VAC). But I want to limit it to a fixed value, which will cause input power derating. To achieve such behavior, one need to saturate the current loop. I think if I can limit the pin 5 "VCOMP" by clamping it to a fixed voltage when line voltage falls below a certain value, the current loop cannot command more than a given value. And if load increases beyond that current value, the output voltage will drop.

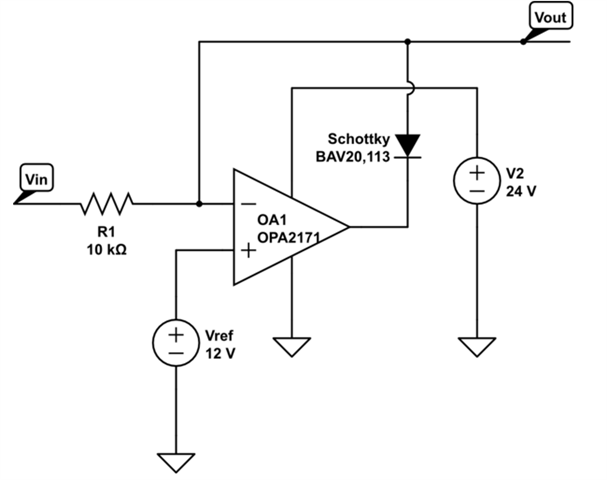

Figure 2: Hardware implementation

Can I implement such circuit to clamp voltage across VCOMP pin? Will it work? Can IC provide enough current for the zener diode? May EDR (enhanced dynamic response) function cause problem? Do you have a solution for such implementation?

best wishes

Süleyman