Other Parts Discussed in Thread: UCC21750

Tool/software:

I'm troubleshooting a half bridge module that uses two UCC21750s. After a few minutes under load, the low side IC will assert the fault pin, stopping operation. On the control side, the fault and reset pins from both ICs are tied together, and this net is pulled up to 3.3v with a 1kOhm resistor. As part of troubleshooting, I've lifted the desat pin off the board and bridged it to the adjacent com pin, to disable the desat circuitry on the low side.

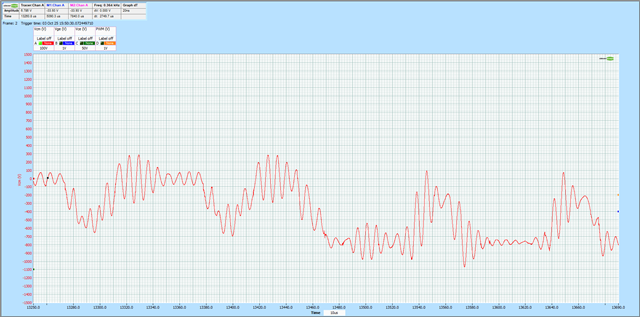

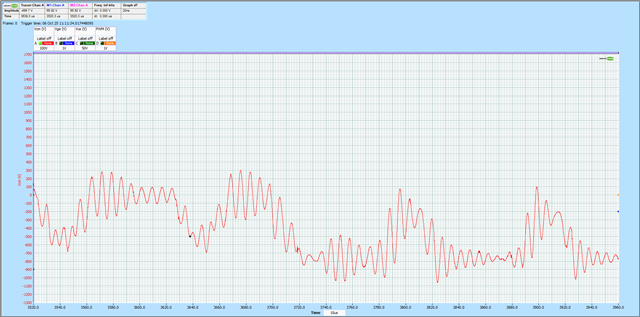

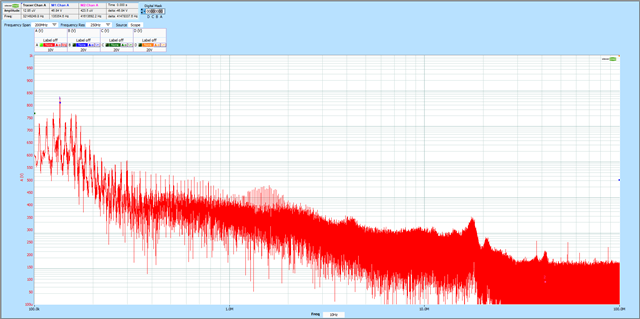

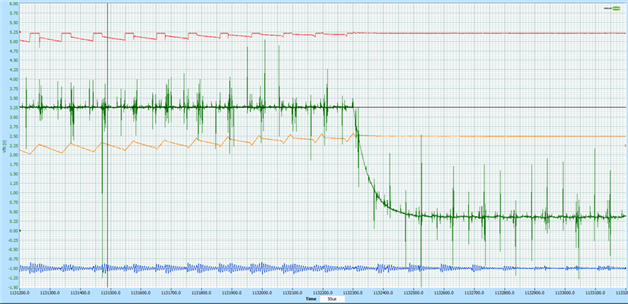

In spite of disabling the desat circuit, the fault pin still goes low after a few minutes. If I lift the low side IC's fault pin off the board, the circuit will operate under load indefinitely. In the scope image below, the green trace is the fault line (250mV/div), red is current through the device that's faulting (50A/div), yellow is the current out the midpoint of the bridge (25A/div), and blue is an unused probe. The timescale is 50us/div. The green probe was a standard 10x probe with a clip lead on it, in a fairly noisy environment. The packaging of the system means I can't use a spring clip or hold a probe in place, sadly.

The only schematic different between the LS and HS is that AIN/APWM are used on the HS to sense module temperature. On the LS, AIN is tied to COM and APWM is floating. The fault consistently occurs on the LS IC.

I've reached the limit of what I can learn from the datasheet, so I'm hoping y'all have some suggestions or insight into what else could be causing the fault pin to go low.