Tool/software:

We are considering using CSD19536KTT FET for 48V BMS.

Charging/discharging specifications are up to 120 A.

In this case, how many FETs should be used in parallel?

May I know an equation for calculating the quantity of FET used?

Tool/software:

We are considering using CSD19536KTT FET for 48V BMS.

Charging/discharging specifications are up to 120 A.

In this case, how many FETs should be used in parallel?

May I know an equation for calculating the quantity of FET used?

Hello Sung Jin Park,

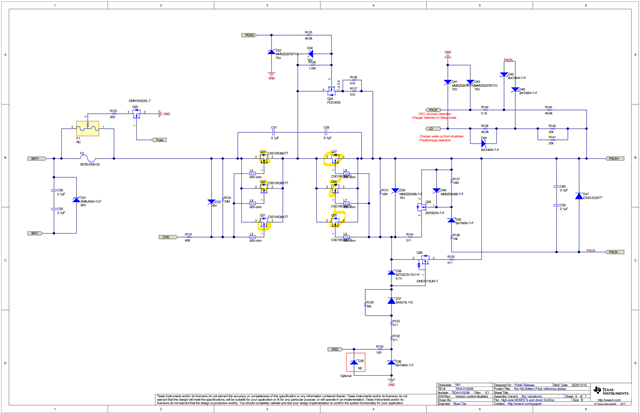

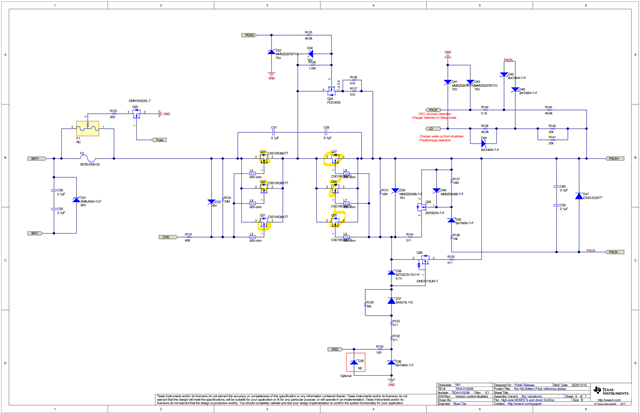

Thanks for your interest in TI FETs. For 120A charge/discharge current, you will need to parallel 4 - 6 FETs for both the charge and discharge devices. You can use the load switch tool at the link below to do your own estimates. The maximum power dissipation capability of the D2PAK package is ~4W on a multilayer PCB with good thermal design. Below is a summary of the calculated power loss in the FETs at 120A and TJ = 125°C.

Load switch tool: https://www.ti.com/tool/LOAD-SWITCH-FET-LOSS-CALC

Best Regards,

John Wallace

TI FET Applications