Tool/software:

Dear TI,

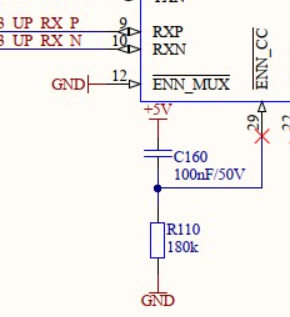

currently we made pre compliance USB tests at Granit River Labs. We use the Microchip Hub USB5708C and the TI MUX HD3SS3220 for the upstream facing port with USB Type C connector. The downstream facing ports are all USB Type A connectors.

Here we got a fail at the test for the upstream facing port.

TD7.01.2 Link Bring-up Test (Subtest 2): The PUT has transmitted more than 6 LFPS after receiving 1 LFPS while the Number of LFPS tx´d before receiving 1 > 18 - the Numer of LFPS tx´d after receiving 1. Gen 1 links should not do this to prevent conflicts with Gen 2 LFPS handshaking.

The downstream facing ports without the mux are working fine.

First i opened a case by microchip. But here finally i got this answer:

You also stated downstream ports are passing this test. Its the same PHY and behavior. the USB3 PHYs don't have any difference whether they are upstream or downstream. So that gives a strong clue that the mux is involved. What does TI say on the matter? I would recommend the customer also open a case to see if this is a known failure.

Do you know this issue with the mux?

Do you have a suggestion to fix this?

Attached is the schematic for the mux and the failure description.

Regards,

Manuel