Tool/software:

Hi All,

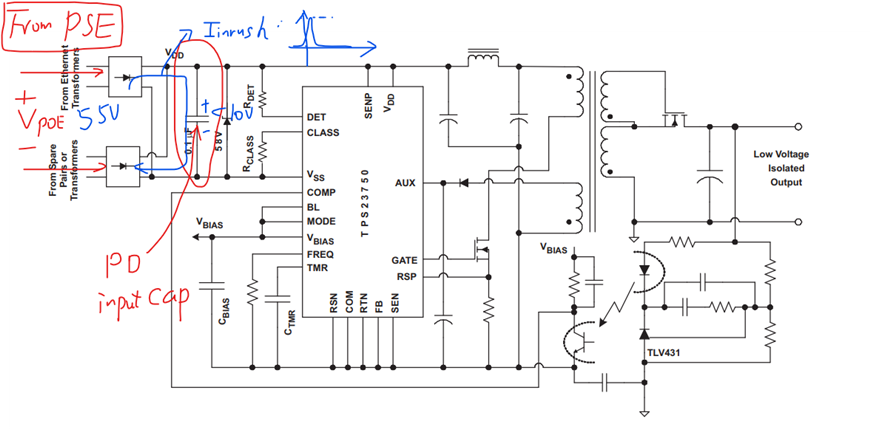

I have a question about the TPS23750.

When VDD is repeatedly turned ON→OFF→ON, an inrush current of about 4A occurs. I would like to confirm whether this can be prevented, or whether the TPS23750 is operating as specified.

(1) First, let me confirm the conditions for the inrush Limit. I understand that the 140mA inrush Limit function activates when VRTN exceeds 12V. Is this correct?

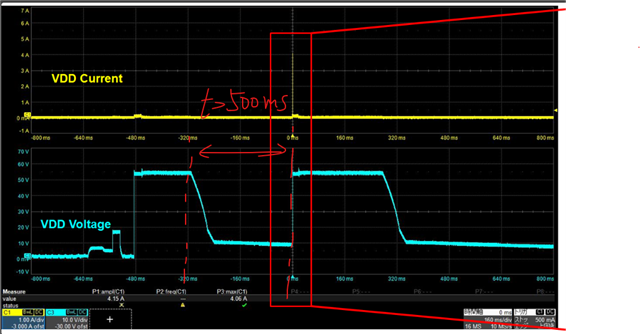

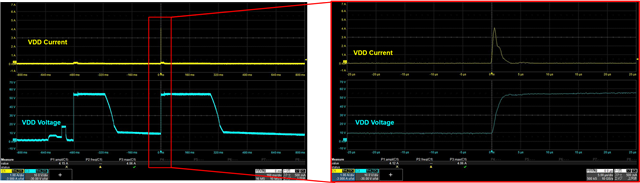

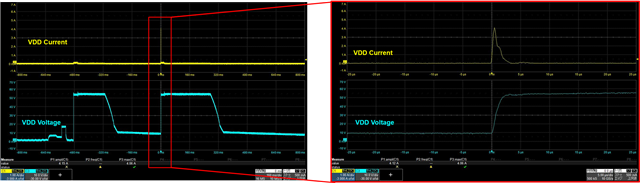

(2) VDD is repeatedly turned ON→OFF→ON. The interval between ON and OFF operations is short.

To be more specific, the power supply hub negotiates to supply 4% power, then immediately turns OFF. When it is turned ON after that, an inrush current of about 4A occurs.

It seems that turning it ON without negotiation prevents the inrush limiter from activating, causing an inrush current occurs.

Below are the waveforms of VDD ON/OFF and the inrush current.

The inrush Limit is not operating. Please explain how this phenomenon works.

Best Regards,

Ishiwata