Tool/software:

Previously, we were using a single chip for data acquisition, and the system was functioning as expected. Recently, we transitioned to a dual-chip setup, which requires using both chip select (CS) lines to communicate with two devices.

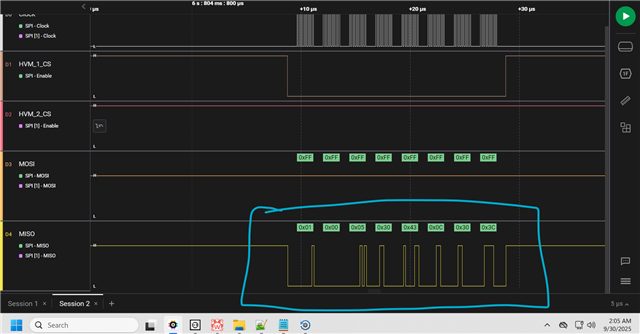

To implement this, I configured two separate TX jobs within a single SPI sequence—each targeting a different CS line. This setup successfully transmits the wake-up signal frames and device configuration frames to both chips, as verified using a logic analyzer.

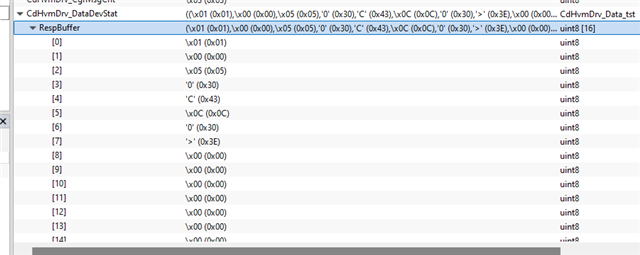

However, the issue arises during the device status read operation. Although the logic analyzer shows the correct frame being transmitted and received, the data observed in the debugger window contains a discrepancy: a single bit is incorrectly set, resulting in a CRC mismatch.

- Expected CRC byte:

0x3C - Received CRC byte:

0x3E

This bit-level deviation is causing the CRC validation to fail, even though the frame appears correct on the logic analyzer.

Additional Notes:

Although this is a brief summary of the issue, I have already tried multiple trial-and-error approaches to resolve it, but none have worked so far. Please feel free to connect with me for a more detailed discussion—I’ll be happy to share all the logs and test cases I’ve tried.