Tool/software:

Hi Experts,

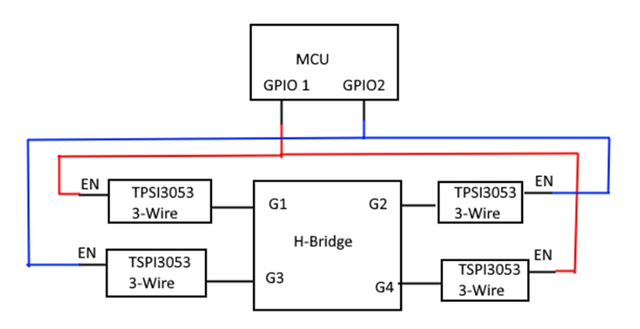

We'd like to confirm if the design below is applicable:

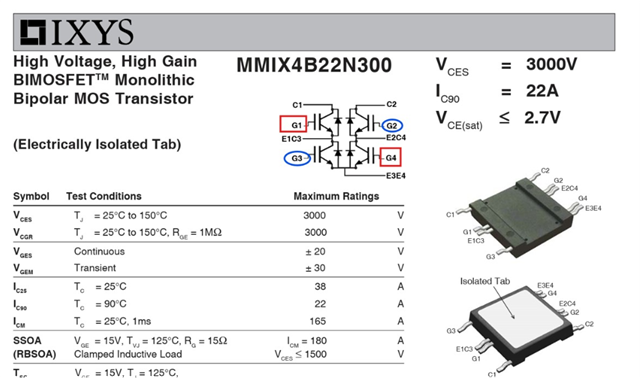

In our application, we are using four TPSI3052QDWZRQ1 devices, one on each gate, to drive gates G1 through G4 on the Littelfuse MMIX4B22N300 H-Bridge. In our application, we drive gates 1-4 and gates 2-3, as pairs.

Question:

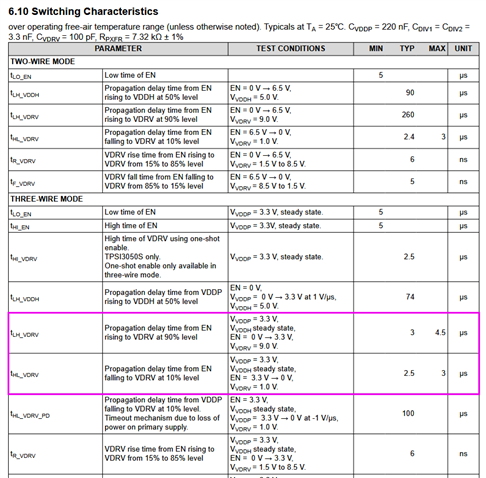

Is there anything incorrect about driving a pair of TPSI3052s configured in three-wire mode, with one MCU GPIO?

According to the datasheet, the EN pin acts as a digital Input configured in a 3-wire mode, and I didn’t see any current consumption of the EN pin when using it in 3-wire mode.

This seems straightforward, but customer wanted TI experts official opinion.

Regards,

Archie A.