Tool/software:

We need support with the TPS767D301PWP LDO regulator implemented in one of our board.

A customer is complaining about unexpected reset generated by the LDO.

The LDO us used with a 5V input voltage to generate 1.9V and 3.3V output voltages.

We made tests with variations of input voltage, and we notice that the reset is generated as soon as the input voltage drop under 4.65V.

According to the datasheet the minimum input voltage is VOUT + Dropout = 3.3V + 0.575 = 3.875V

Can you help us to understand why we have this reset generated at 4.65V ?

The output voltages are still working correctly when the reset is generated.

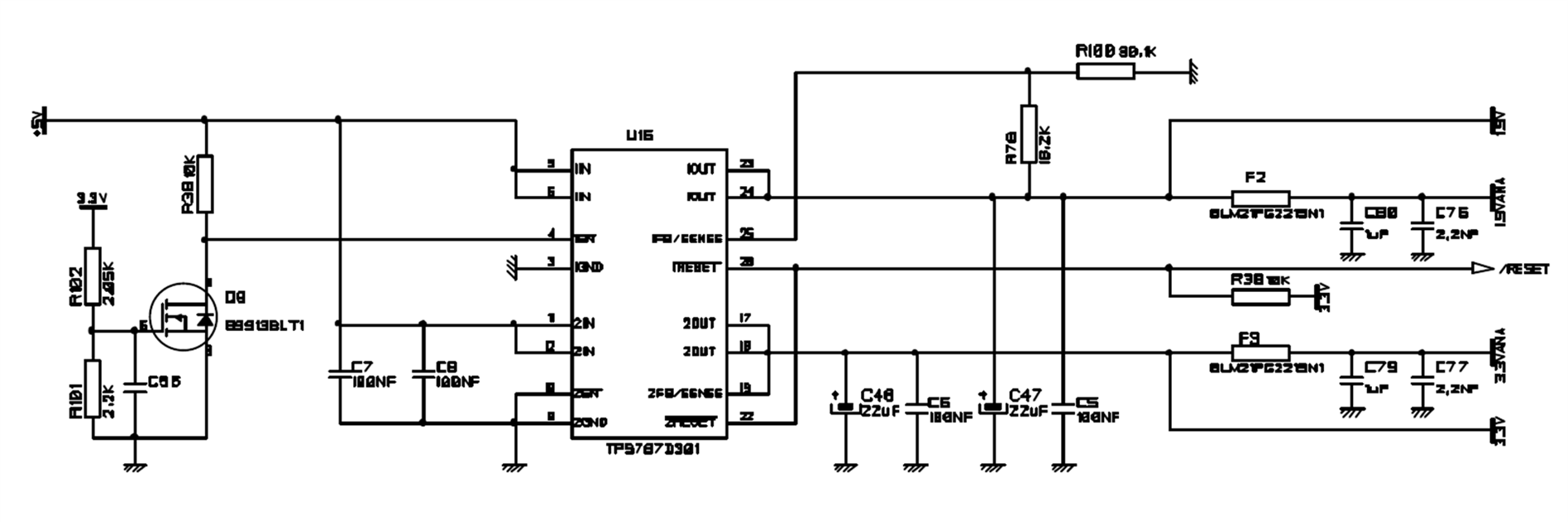

Below the implementation of the LDO in our board :