Tool/software:

Hi,

I have a question regarding the use of this MOSFET in a current-limiting application:

-

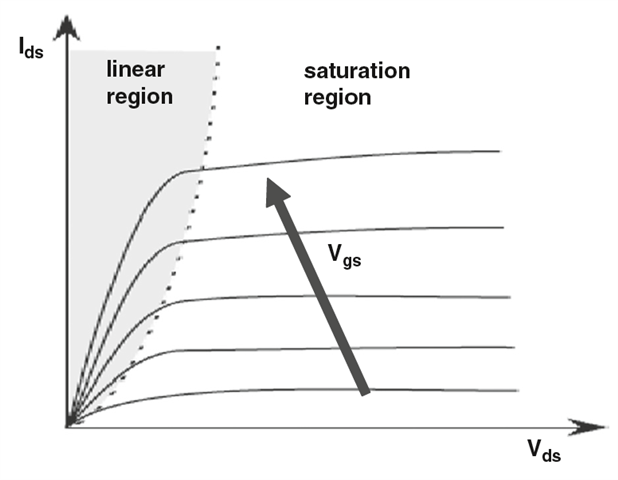

Under normal conditions, when the current is below the limit threshold, the MOSFET should operate in the linear (or constant resistance) region, with the gate voltage adjusting according to the drain current. If I am sensing the drain current, how can I set the gate voltage correctly to keep the MOSFET in the linear region while minimizing power dissipation?

-

When the current reaches the threshold and I want to limit it to a constant value for a predetermined time, the MOSFET should enter saturation. How can I adjust the gate voltage to ensure the MOSFET operates in saturation in this case?

Best regards,

Mohamed