Tool/software:

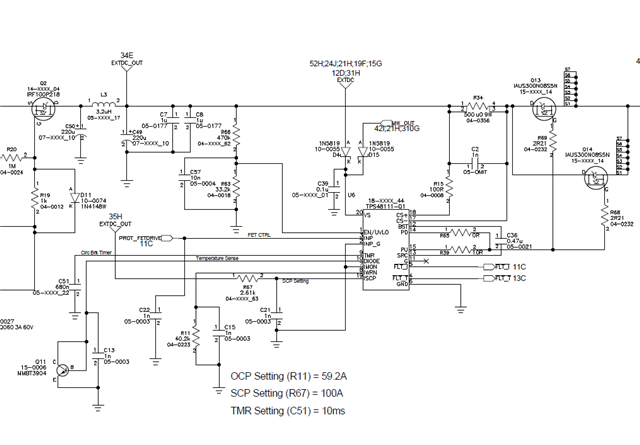

Page 3 of this schematic shows implementation of TPS48111-Q1.

With C13, C15, C51 shorted that should disable overcurrent & temperature fault.

I also have R67 + C21 removed, and a wire from R67.2 to C2.2 to disable short circuit protection.

There is a wire connecting C36.2 to Q13 SRC.

INP has a 3.16k pull-up to 5V. EN/UVLO is referenced to EXTDC not EXTDC_OUT.

When EXTDC is applied, the chip should be powered and charge pump enabled (I see this). As soon as the charge pump passes BST_UVLOR, the FETs enable but immediately shut off. I see FLT_I still trip from HI - LO.

Can nuisance / false trips still occur with all of the protections disabled? Am I missing something?