Tool/software:

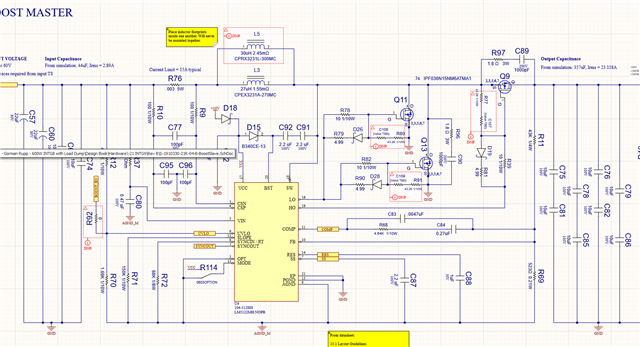

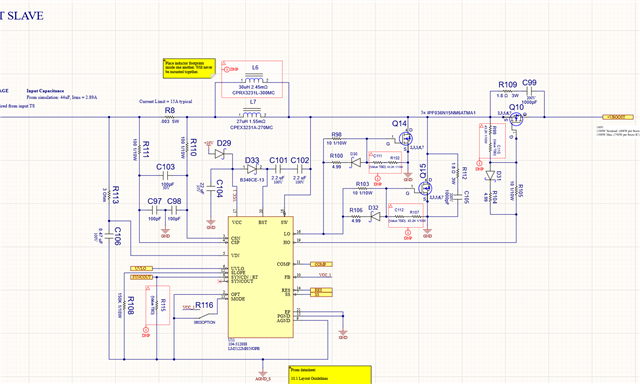

I currently have a 1500W boost design using a pair of LM5122. I'm boosting from a nominal input of 48V to 100V out.

Generally, I have things working pretty well, however occasionally I'm seeing a failure that so far has been hard to narrow down. When the failure occurs, I generally lose all my FETs (high and low side) as well as the LM5122 ICs. I'm not sure which fails first but I'm starting to question if the issue is with the SW pin. I see there is an absolute max of 105V on that pin, referenced to AGND. The datasheet says the part is designed to boost up to 100V but I that margin seems very close for comfort.

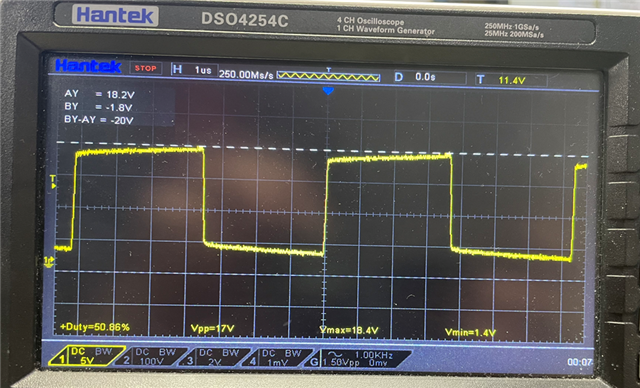

I get a very stable 99-100V output after the high side FETs (at my bulk capacitance) but I see above 100V at the SW pin.

Do you have any recommendations for ensuring the SW pin doesn't see more than 105V when boosting to 100V? Or should this part actually be avoided when needed 100V out?