Tool/software:

Hi,

Following the discussion in this thread: TPS63900: Supercap charging

We use a Supercapacitor as our main energy storage element. It is mainly charged by solar power, but should also be charged with a primary battery as a backup.

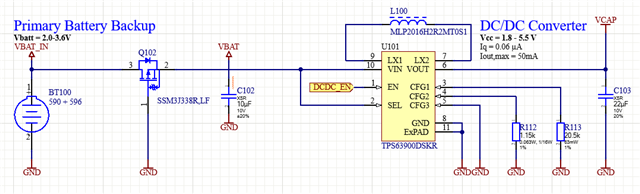

For this we use the following circuit (the supercap is not shown, but is connected to VCAP), which charges the Supercapacitor up to 3V, whenever it should fall below that threshold. The supercap voltage can also be higher, if it is charged by solar.

Can you please confirm that the schematic shown is correct?

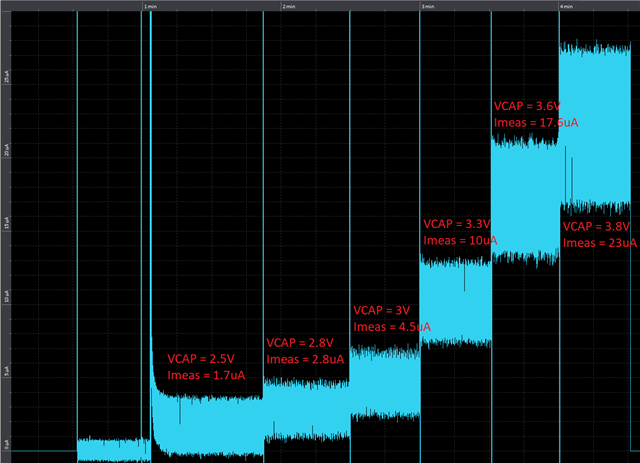

However, the circuit should also be usable if no backup battery is inserted (VBAT_IN is floating). But right now I measure a large reverse current going into the VOUT pin of the TPS63900, depending on the supercap voltage up to 23uA at VCAP = 3.8V.

Is this behaviour normal? Can the reverse current flowing into the TPS63900 be avoided?