Tool/software:

I am evaluating the LM5012 in a buck converter design and comparing my results with the datasheet application curves.

Figure 9-5 in the datasheet shows a much faster transient response than I am observing. Can you confirm what output capacitance was used in those measurements?

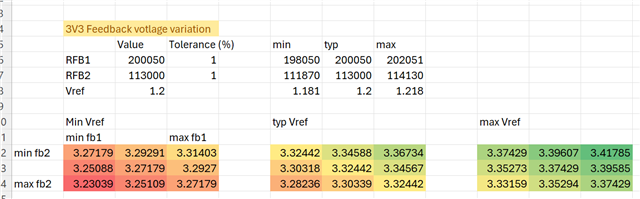

With a 0-2 A load step (2 µs edge rate), my circuit shows:

- Overshoot to about 3.7 V on a 3.3 V rail when the load returns to 0 A.

- Settling time of roughly 700 µs.

This looks quite a bit slower than the datasheet plot, so I wanted to check if I might be missing something in my setup or compensation.

Thanks!