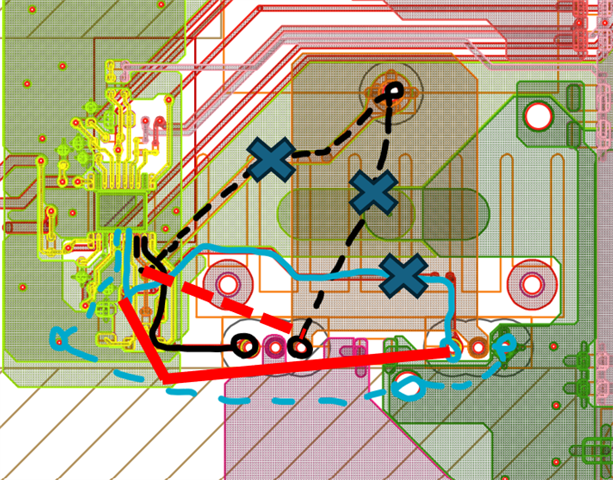

Hello. I am currently designing a circuit using the LM5122. I have built a prototype based on the attached schematic and am in the process of verifying its operation.

The input voltage is set to 24 V, and the target output is 53 V / 15.1 A. The circuit operates normally up to 10 A output, but when the output current reaches around 11 A, abnormal switching behavior occurs.

Could you please review the design and let me know if there are any issues or improvements I should consider?

I have attached the waveforms of Q600 (CH2) and Q601 (CH1) at 10 A and 11 A output conditions.

circuit.pdf

Thank you for your support.

Best regards,

Nomura