Other Parts Discussed in Thread: LM5137

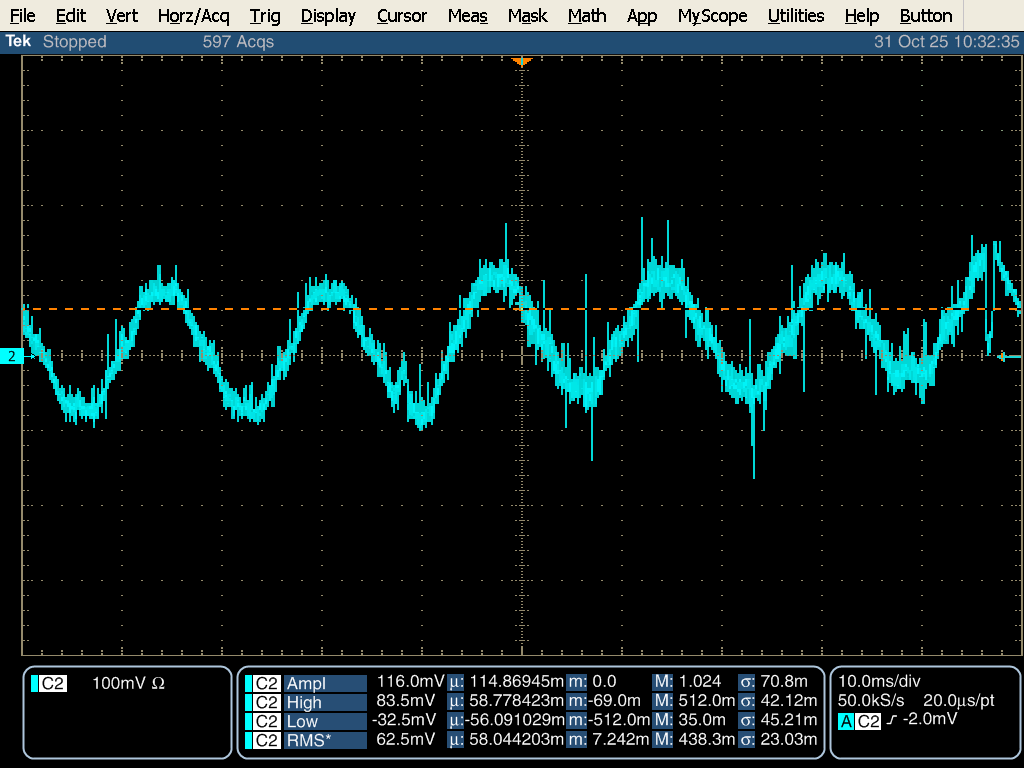

I am using the LM5137F-Q1 with:

- 24-42V input

- 12V output (set via feedback resistors)

- DRSS 10%

- FPWM enabled

- 0.5ohm load resistor (~24A total load current)

I'm seeing ~20% higher current being sourced from the secondary channel, where I would expect equal loading to primary and secondary.

What could be possible causes to look for? Is this purely layout related?