Hi,

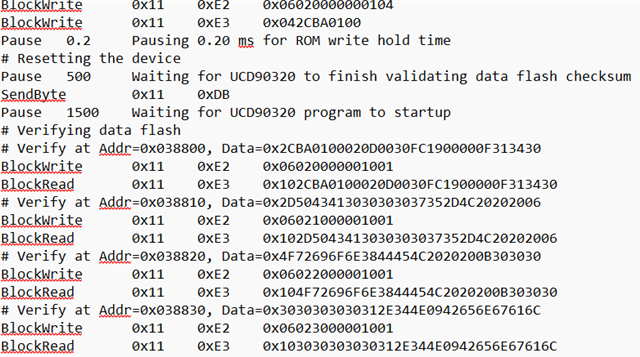

We are trying to remote upgrade the UCD90320 firmware through PMBUS script exported from the Fusion Digital Tool. The observations are as follows,The programming get's completed without any issue and the new firmware comes into effect after power-cycle.The soft reset command 0xDB is sent at the end of the script for firmware reset and we are reading the version register 9Bh after powercycle to verify the change in the version number.

However, at times the device gets corrupted after issuing the 0xDB command for firmware reset.Let us know what we are missing out?