Hello

My design comprises a SEPIC stage with 4V5-20V input range and 13.5V output at max. 1A. In most cases the load is significantly lighter, coming down to a 0.5W minimum instead of 13.5W.

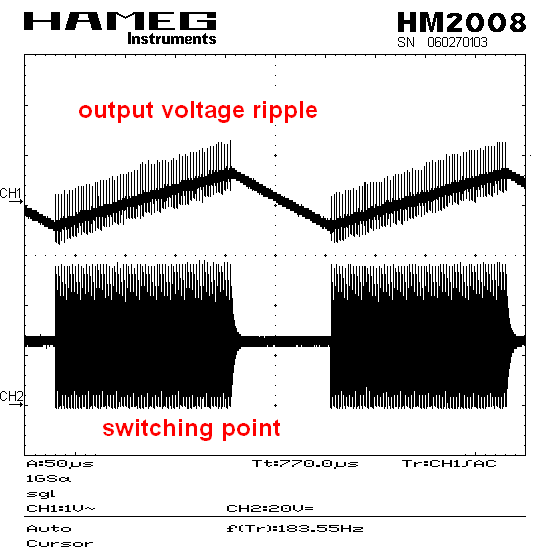

In these conditions there is a strange regulation behaviour seen for higher input voltages. Everything is fine for Vin below 16V. At about 16V5 the regulation gets jumpy with noise in the lower kHz-range. Furthermore, the average output voltage rises to 14.5V, meaning, that the feedback input is almost permanently above 1.25V (a voltmeter reads 1.30V average).

I varied in large scales the capacitor at the feedback pin (usually 100pF to GND) and the capacitor-resistor series from COMP to GND, all to no avail. The scene does change as soon as the load increases a little. However: the total load is controlled by uController (turning on/off parts of the circuit) and is always kept at minimum.

Compare the two images in the attached file with 12V input (everything OK) and 18V (with 2kHz ON/OFF alternation).

Where do I have to look at to make this (or a similar) design stable for light loads?

Thanks and regards

Thomas