Dear E2E:

Thank you for your help.

I use TPS65070 to power OMAP-L138. Everything looks good and works OK.

I use also embedded ADC converter for the different voltages measurement and this also works OK.

I have the question about possible accidental power shutdown by the SW through I2C0 interface.

1. I use AC power (5V) input Pin10.

2. In the DS page43 - Register PPATH1 bit[4] "AC power enable" can be set ='1' to disable AC power input.

3. What is going to happen if SW accidently set PPATH1_bit[4]=1 (AC power input is disabled)? It is not clear from the data sheet but since AC input is the only one power source - all DCDC converter outputs will be shutdown. Is this correct?

4. How the system can recover from this "shutdown"?

5. AC input will still have +5V active and POWER_ON input is still high. Will TPS65070 restart again with default values? It is not clear from the data sheet.

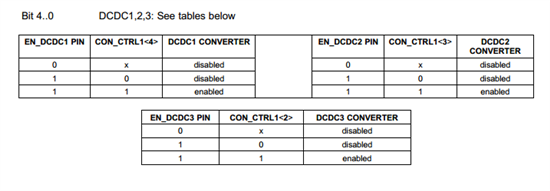

6. In DS page53 - Con_CTRL1 register bit[4:2] for DCDC1:DCDC3. It is not exactly clear - now these enable bits function.

7. DCDC2 and DCDC3 are automatically power-up sequencing. So the enable pins for DCDC2 and DCDC3 are tired to GND (page53). "The CON_CTRL1 Bits are automatically reset to default when the corresponding enable pin is low". How to understand that? Does it mean - the DCDC2 and DCDC3 will restart again after being disabled by writing '0' to bit[3:2]. Or according to the Tables on page54 - the state of bit[3:2] don't care?

8. EN_DCDC1 pin controls the DCDC1 since [DCDC_SQ2:DCDC_SQ0] bits[7:5]=011. DCD1 is not the part of automatic sequencing. In this case CON_CTRL1_bit[4] can disable DCDC1. Is it correct?

9. Will DCDC1 restart again after that automatically? What is required to restart the DCDC1?

Thank you very much for your help,

Boris Ruvinsky